Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

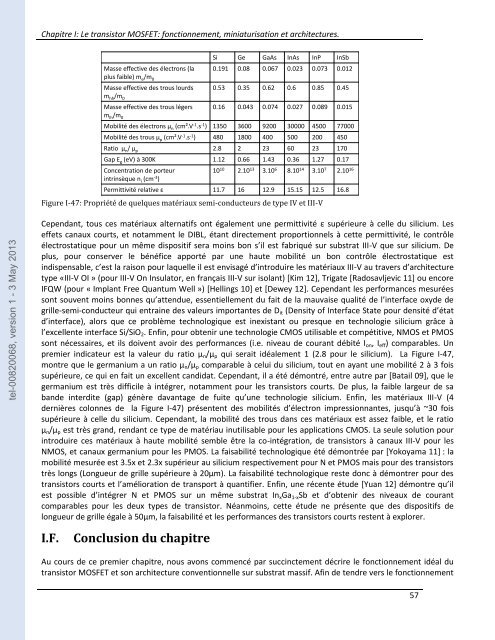

Chapitre I: Le transistor MOSFET: fonctionnement, miniaturisation et architectures.<br />

Si Ge GaAs InAs InP InSb<br />

Masse effective <strong>de</strong>s électrons (la 0.191 0.08 0.067 0.023 0.073 0.012<br />

plus faible) m e /m 0<br />

Masse effective <strong>de</strong>s trous lourds 0.53 0.35 0.62 0.6 0.85 0.45<br />

m hh /m 0<br />

Masse effective <strong>de</strong>s trous légers 0.16 0.043 0.074 0.027 0.089 0.015<br />

m lh /m 0<br />

Mobilité <strong>de</strong>s électrons µ n (cm².V -1 .s -1 ) 1350 3600 9200 30000 4500 77000<br />

Mobilité <strong>de</strong>s trous µ p (cm².V -1 .s -1 ) 480 1800 400 500 200 450<br />

Ratio µ n / µ p 2.8 2 23 60 23 170<br />

Gap E g (eV) à 300K 1.12 0.66 1.43 0.36 1.27 0.17<br />

Concentration <strong>de</strong> porteur<br />

intrinsèque n i (cm -3 )<br />

10 10 2.10 13 3.10 6 8.10 14 3.10 7 2.10 16<br />

Permittivité relative ε 11.7 16 12.9 15.15 12.5 16.8<br />

Figure I-47: Propriété <strong>de</strong> quelques matériaux semi-conducteurs <strong>de</strong> type IV et III-V<br />

tel-00820068, version 1 - 3 May 2013<br />

Cependant, tous ces matériaux alternatifs ont également une permittivité ε supérieure à celle du silicium. Les<br />

effets canaux courts, et notamment le DIBL, étant directement proportionnels à cette permittivité, le contrôle<br />

électrostatique <strong>pour</strong> un même dispositif sera moins bon s’il est fabriqué sur substrat III-V que sur silicium. De<br />

plus, <strong>pour</strong> conserver le bénéfice apporté par une haute mobilité un bon contrôle électrostatique est<br />

indispensable, c’est la raison <strong>pour</strong> laquelle il est envisagé d’introduire les matériaux III-V au travers d’architecture<br />

type «III-V OI » (<strong>pour</strong> III-V On Insulator, en français III-V sur isolant) [Kim 12], Trigate [Radosavljevic 11] ou encore<br />

IFQW (<strong>pour</strong> « Implant Free Quantum Well ») [Hellings 10] et [Dewey 12]. Cependant les <strong>performances</strong> mesurées<br />

sont souvent moins bonnes qu’attendue, essentiellement du fait <strong>de</strong> la mauvaise qualité <strong>de</strong> l’interface oxy<strong>de</strong> <strong>de</strong><br />

grille-semi-conducteur qui entraine <strong>de</strong>s valeurs importantes <strong>de</strong> D it (Density of Interface State <strong>pour</strong> <strong>de</strong>nsité d’état<br />

d’interface), alors que ce problème technologique est inexistant ou presque en technologie silicium grâce à<br />

l’excellente interface Si/SiO 2 . Enfin, <strong>pour</strong> obtenir une technologie CMOS utilisable et compétitive, NMOS et PMOS<br />

sont nécessaires, et ils doivent avoir <strong>de</strong>s <strong>performances</strong> (i.e. niveau <strong>de</strong> courant débité I on , I eff ) comparables. Un<br />

premier indicateur est la valeur du ratio µ n /µ p qui serait idéalement 1 (2.8 <strong>pour</strong> le silicium). La Figure I-47,<br />

montre que le germanium a un ratio µ n /µ p comparable à celui du silicium, tout en ayant une mobilité 2 à 3 fois<br />

supérieure, ce qui en fait un excellent candidat. Cependant, il a été démontré, entre autre par [Batail 09], que le<br />

germanium est très difficile à intégrer, notamment <strong>pour</strong> les transistors courts. De plus, la faible largeur <strong>de</strong> sa<br />

ban<strong>de</strong> interdite (gap) génère davantage <strong>de</strong> fuite qu’une technologie silicium. Enfin, les matériaux III-V (4<br />

<strong>de</strong>rnières colonnes <strong>de</strong> la Figure I-47) présentent <strong>de</strong>s mobilités d’électron impressionnantes, jusqu’à ~30 fois<br />

supérieure à celle du silicium. Cependant, la mobilité <strong>de</strong>s trous dans ces matériaux est assez faible, et le ratio<br />

µ n /µ p est très grand, rendant ce type <strong>de</strong> matériau inutilisable <strong>pour</strong> les applications CMOS. La seule solution <strong>pour</strong><br />

introduire ces matériaux à haute mobilité semble être la co-intégration, <strong>de</strong> transistors à canaux III-V <strong>pour</strong> les<br />

NMOS, et canaux germanium <strong>pour</strong> les PMOS. La faisabilité technologique été démontrée par [Yokoyama 11] : la<br />

mobilité mesurée est 3.5x et 2.3x supérieur au silicium respectivement <strong>pour</strong> N et PMOS mais <strong>pour</strong> <strong>de</strong>s transistors<br />

très longs (Longueur <strong>de</strong> grille supérieure à 20µm). La faisabilité technologique reste donc à démontrer <strong>pour</strong> <strong>de</strong>s<br />

transistors courts et l’amélioration <strong>de</strong> transport à quantifier. Enfin, une récente étu<strong>de</strong> [Yuan 12] démontre qu’il<br />

est possible d’intégrer N et PMOS sur un même substrat In x Ga 1-x Sb et d’obtenir <strong>de</strong>s niveaux <strong>de</strong> courant<br />

comparables <strong>pour</strong> les <strong>de</strong>ux types <strong>de</strong> transistor. Néanmoins, cette étu<strong>de</strong> ne présente que <strong>de</strong>s dispositifs <strong>de</strong><br />

longueur <strong>de</strong> grille égale à 50µm, la faisabilité et les <strong>performances</strong> <strong>de</strong>s transistors courts restent à explorer.<br />

I.F.<br />

Conclusion du chapitre<br />

Au cours <strong>de</strong> ce premier chapitre, nous avons commencé par succinctement décrire le fonctionnement idéal du<br />

transistor MOSFET et son architecture conventionnelle sur substrat massif. Afin <strong>de</strong> tendre vers le fonctionnement<br />

57