Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Architecture CMOS<br />

Chapitre I: Le transistor MOSFET: fonctionnement, miniaturisation et architectures.<br />

tel-00820068, version 1 - 3 May 2013<br />

I.E.<br />

Vers <strong>de</strong> nouvelles architectures<br />

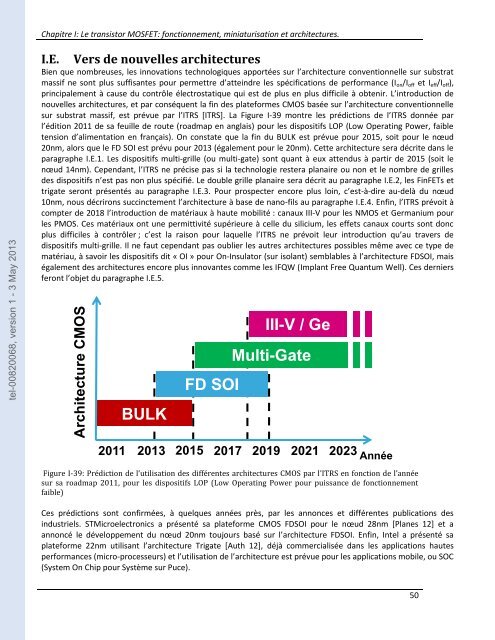

Bien que nombreuses, les innovations technologiques apportées sur l’architecture conventionnelle sur substrat<br />

massif ne sont plus suffisantes <strong>pour</strong> permettre d’atteindre les spécifications <strong>de</strong> performance (I on /I off et I eff /I off ),<br />

principalement à cause du contrôle électrostatique qui est <strong>de</strong> plus en plus difficile à obtenir. L’introduction <strong>de</strong><br />

nouvelles architectures, et par conséquent la fin <strong>de</strong>s plateformes CMOS basée sur l’architecture conventionnelle<br />

sur substrat massif, est prévue par l’ITRS [ITRS]. La Figure I-39 montre les prédictions <strong>de</strong> l’ITRS donnée par<br />

l’édition 2011 <strong>de</strong> sa feuille <strong>de</strong> route (roadmap en anglais) <strong>pour</strong> les dispositifs LOP (Low Operating Power, faible<br />

tension d’alimentation en français). On constate que la fin du BULK est prévue <strong>pour</strong> 2015, soit <strong>pour</strong> le nœud<br />

20nm, alors que le FD SOI est prévu <strong>pour</strong> 2013 (également <strong>pour</strong> le 20nm). Cette architecture sera décrite dans le<br />

paragraphe I.E.1. Les dispositifs multi-grille (ou multi-gate) sont quant à eux attendus à partir <strong>de</strong> 2015 (soit le<br />

nœud 14nm). Cependant, l’ITRS ne précise pas si la technologie restera planaire ou non et le nombre <strong>de</strong> grilles<br />

<strong>de</strong>s dispositifs n’est pas non plus spécifié. Le double grille planaire sera décrit au paragraphe I.E.2, les FinFETs et<br />

trigate seront présentés au paragraphe I.E.3. Pour prospecter encore plus loin, c’est-à-dire au-<strong>de</strong>là du nœud<br />

10nm, nous décrirons succinctement l’architecture à base <strong>de</strong> nano-fils au paragraphe I.E.4. Enfin, l’ITRS prévoit à<br />

compter <strong>de</strong> 2018 l’introduction <strong>de</strong> matériaux à haute mobilité : canaux III-V <strong>pour</strong> les NMOS et Germanium <strong>pour</strong><br />

les PMOS. Ces matériaux ont une permittivité supérieure à celle du silicium, les effets canaux courts sont donc<br />

plus difficiles à contrôler ; c’est la raison <strong>pour</strong> laquelle l’ITRS ne prévoit leur introduction qu’au travers <strong>de</strong><br />

dispositifs multi-grille. Il ne faut cependant pas oublier les autres architectures possibles même avec ce type <strong>de</strong><br />

matériau, à savoir les dispositifs dit « OI » <strong>pour</strong> On-Insulator (sur isolant) semblables à l’architecture FDSOI, mais<br />

également <strong>de</strong>s architectures encore plus innovantes comme les IFQW (Implant Free Quantum Well). Ces <strong>de</strong>rniers<br />

feront l’objet du paragraphe I.E.5.<br />

BULK<br />

FD SOI<br />

III-V / Ge<br />

Multi-Gate<br />

2011 2013 2015 2017 2019 2021 2023 Année<br />

Figure I-39: Prédiction <strong>de</strong> l’utilisation <strong>de</strong>s différentes architectures CMOS par l’ITRS en fonction <strong>de</strong> l’année<br />

sur sa roadmap 2011, <strong>pour</strong> les dispositifs LOP (Low Operating Power <strong>pour</strong> puissance <strong>de</strong> fonctionnement<br />

faible)<br />

Ces prédictions sont confirmées, à quelques années près, par les annonces et différentes publications <strong>de</strong>s<br />

industriels. STMicroelectronics a présenté sa plateforme CMOS FDSOI <strong>pour</strong> le nœud 28nm [Planes 12] et a<br />

annoncé le développement du nœud 20nm toujours basé sur l’architecture FDSOI. Enfin, Intel a présenté sa<br />

plateforme 22nm utilisant l’architecture Trigate [Auth 12], déjà commercialisée dans les applications hautes<br />

<strong>performances</strong> (micro-processeurs) et l’utilisation <strong>de</strong> l’architecture est prévue <strong>pour</strong> les applications mobile, ou SOC<br />

(System On Chip <strong>pour</strong> Système sur Puce).<br />

50