Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapitre I: Le transistor MOSFET: fonctionnement, miniaturisation et architectures.<br />

I.D. Solutions technologiques <strong>pour</strong> <strong>pour</strong>suivre la course à la<br />

miniaturisation<br />

Dans cette partie, nous allons décrire les améliorations technologiques nécessaires à l’architecture<br />

conventionnelle sur substrat massif afin <strong>de</strong> pouvoir <strong>pour</strong>suivre la réduction <strong>de</strong> ses dimensions sans être trop<br />

impactée par les effets parasites décrits au paragraphe précé<strong>de</strong>nt.<br />

I.D.1.<br />

Ingénierie <strong>de</strong> jonction<br />

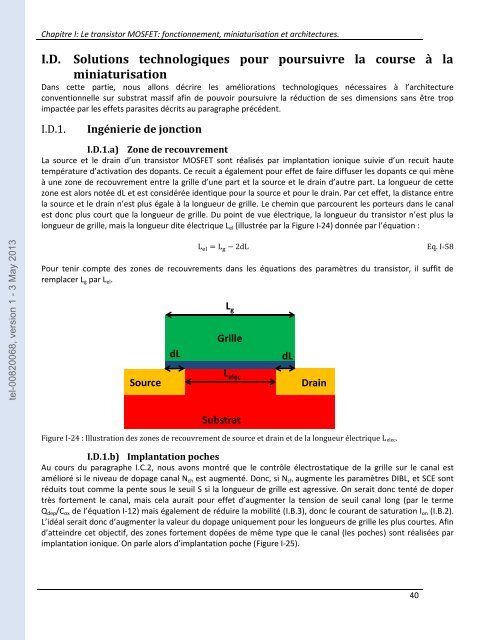

I.D.1.a) Zone <strong>de</strong> recouvrement<br />

La source et le drain d’un transistor MOSFET sont réalisés par implantation ionique suivie d’un recuit haute<br />

température d’activation <strong>de</strong>s dopants. Ce recuit a également <strong>pour</strong> effet <strong>de</strong> faire diffuser les dopants ce qui mène<br />

à une zone <strong>de</strong> recouvrement entre la grille d’une part et la source et le drain d’autre part. La longueur <strong>de</strong> cette<br />

zone est alors notée dL et est considérée i<strong>de</strong>ntique <strong>pour</strong> la source et <strong>pour</strong> le drain. Par cet effet, la distance entre<br />

la source et le drain n’est plus égale à la longueur <strong>de</strong> grille. Le chemin que parcourent les porteurs dans le canal<br />

est donc plus court que la longueur <strong>de</strong> grille. Du point <strong>de</strong> vue électrique, la longueur du transistor n’est plus la<br />

longueur <strong>de</strong> grille, mais la longueur dite électrique L el (illustrée par la Figure I-24) donnée par l’équation :<br />

tel-00820068, version 1 - 3 May 2013<br />

Eq. I-58<br />

Pour tenir compte <strong>de</strong>s zones <strong>de</strong> recouvrements dans les équations <strong>de</strong>s paramètres du transistor, il suffit <strong>de</strong><br />

remplacer L g par L el .<br />

Source<br />

dL<br />

L g<br />

Grille<br />

L elec<br />

dL<br />

Drain<br />

Substrat<br />

Figure I-24 : Illustration <strong>de</strong>s zones <strong>de</strong> recouvrement <strong>de</strong> source et drain et <strong>de</strong> la longueur électrique L elec.<br />

I.D.1.b) Implantation poches<br />

Au cours du paragraphe I.C.2, nous avons montré que le contrôle électrostatique <strong>de</strong> la grille sur le canal est<br />

amélioré si le niveau <strong>de</strong> dopage canal N ch est augmenté. Donc, si N ch augmente les paramètres DIBL, et SCE sont<br />

réduits tout comme la pente sous le seuil S si la longueur <strong>de</strong> grille est agressive. On serait donc tenté <strong>de</strong> doper<br />

très fortement le canal, mais cela aurait <strong>pour</strong> effet d’augmenter la tension <strong>de</strong> seuil canal long (par le terme<br />

Q <strong>de</strong>p /C ox <strong>de</strong> l’équation I-12) mais également <strong>de</strong> réduire la mobilité (I.B.3), donc le courant <strong>de</strong> saturation I on (I.B.2).<br />

L’idéal serait donc d’augmenter la valeur du dopage uniquement <strong>pour</strong> les longueurs <strong>de</strong> grille les plus courtes. Afin<br />

d’atteindre cet objectif, <strong>de</strong>s zones fortement dopées <strong>de</strong> même type que le canal (les poches) sont réalisées par<br />

implantation ionique. On parle alors d’implantation poche (Figure I-25).<br />

40