Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

Développement de modèles pour l'évaluation des performances ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Chapitre I: Le transistor MOSFET: fonctionnement, miniaturisation et architectures.<br />

Ce chapitre a <strong>pour</strong> objectif <strong>de</strong> définir les différents concepts théoriques et les paramètres relatifs au transistor<br />

MOSFET (Métal-Oxy<strong>de</strong>-Semiconducteur). Nous commencerons par décrire l’architecture conventionnelle sur<br />

substrat massif classique (BULK) idéal, c’est-à-dire sans aucun effet parasite. Ensuite, nous expliciterons les effets<br />

<strong>de</strong> la course à la miniaturisation sur le fonctionnement du transistor MOSFET idéal. Nous détaillerons par la suite<br />

les solutions technologiques apportées à l’architecture conventionnelle sur substrat massif classique <strong>pour</strong> lutter<br />

contre ces effets, dits « parasites ». Enfin, la réduction <strong>de</strong>s dimensions <strong>de</strong> nœuds en nœuds <strong>de</strong> l’architecture<br />

conventionnelle sur substrat massif ne procurant plus suffisamment <strong>de</strong> gain en performance, nous décrirons les<br />

nouvelles architectures <strong>de</strong> transistor MOSFET envisagées.<br />

I.A. Le Transistor MOSFET idéal<br />

tel-00820068, version 1 - 3 May 2013<br />

I.A.1.<br />

Principe <strong>de</strong> fonctionnement<br />

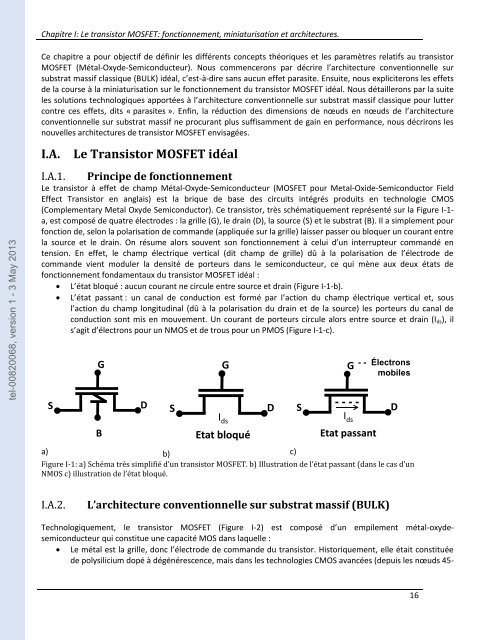

Le transistor à effet <strong>de</strong> champ Métal-Oxy<strong>de</strong>-Semiconducteur (MOSFET <strong>pour</strong> Metal-Oxi<strong>de</strong>-Semiconductor Field<br />

Effect Transistor en anglais) est la brique <strong>de</strong> base <strong>de</strong>s circuits intégrés produits en technologie CMOS<br />

(Complementary Metal Oxy<strong>de</strong> Semiconductor). Ce transistor, très schématiquement représenté sur la Figure I-1-<br />

a, est composé <strong>de</strong> quatre électro<strong>de</strong>s : la grille (G), le drain (D), la source (S) et le substrat (B). Il a simplement <strong>pour</strong><br />

fonction <strong>de</strong>, selon la polarisation <strong>de</strong> comman<strong>de</strong> (appliquée sur la grille) laisser passer ou bloquer un courant entre<br />

la source et le drain. On résume alors souvent son fonctionnement à celui d’un interrupteur commandé en<br />

tension. En effet, le champ électrique vertical (dit champ <strong>de</strong> grille) dû à la polarisation <strong>de</strong> l’électro<strong>de</strong> <strong>de</strong><br />

comman<strong>de</strong> vient moduler la <strong>de</strong>nsité <strong>de</strong> porteurs dans le semiconducteur, ce qui mène aux <strong>de</strong>ux états <strong>de</strong><br />

fonctionnement fondamentaux du transistor MOSFET idéal :<br />

L’état bloqué : aucun courant ne circule entre source et drain (Figure I-1-b).<br />

L’état passant : un canal <strong>de</strong> conduction est formé par l’action du champ électrique vertical et, sous<br />

l’action du champ longitudinal (dû à la polarisation du drain et <strong>de</strong> la source) les porteurs du canal <strong>de</strong><br />

conduction sont mis en mouvement. Un courant <strong>de</strong> porteurs circule alors entre source et drain (I ds ), il<br />

s’agit d’électrons <strong>pour</strong> un NMOS et <strong>de</strong> trous <strong>pour</strong> un PMOS (Figure I-1-c).<br />

S<br />

G<br />

B<br />

D<br />

a) b) c)<br />

S<br />

G<br />

- - - -<br />

D S D<br />

I ds<br />

Etat bloqué<br />

Figure I-1: a) Schéma très simplifié d’un transistor MOSFET. b) Illustration <strong>de</strong> l’état passant (dans le cas d’un<br />

NMOS c) illustration <strong>de</strong> l’état bloqué.<br />

G<br />

I ds<br />

Etat passant<br />

- - Électrons<br />

mobiles<br />

I.A.2.<br />

L’architecture conventionnelle sur substrat massif (BULK)<br />

Technologiquement, le transistor MOSFET (Figure I-2) est composé d’un empilement métal-oxy<strong>de</strong>semiconducteur<br />

qui constitue une capacité MOS dans laquelle :<br />

Le métal est la grille, donc l’électro<strong>de</strong> <strong>de</strong> comman<strong>de</strong> du transistor. Historiquement, elle était constituée<br />

<strong>de</strong> polysilicium dopé à dégénérescence, mais dans les technologies CMOS avancées (<strong>de</strong>puis les nœuds 45-<br />

16