mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

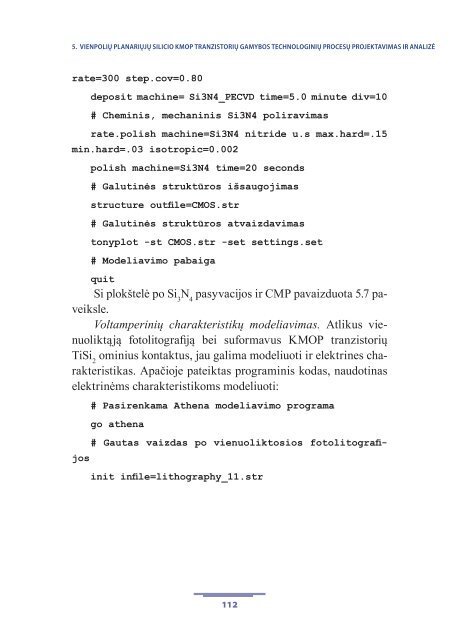

5. VIENPOLIŲ PLANARIŲJŲ SILICIO KMOP TRANZISTORIŲ GAMYBOS TECHNOLOGINIŲ PROCESŲ PROJEKTAVIMAS IR ANALIZĖ<br />

rate=300 step.cov=0.80<br />

deposit machine= Si3N4_PECVD time=5.0 minute div=10<br />

# Cheminis, mechaninis Si3N4 poliravimas<br />

rate.polish machine=Si3N4 nitride u.s max.hard=.15<br />

min.hard=.03 isotropic=0.002<br />

polish machine=Si3N4 time=20 seconds<br />

# Galutinės struktūros išsaugojimas<br />

structure outfile=CMOS.str<br />

# Galutinės struktūros atvaizdavimas<br />

tonyplot -st CMOS.str -set settings.set<br />

# Modeliavimo pabaiga<br />

quit<br />

Si plokštelė po Si 3<br />

N 4<br />

pasyvacijos ir CMP pavaizduota 5.7 paveiksle.<br />

Voltamperinių charakteristikų modeliavimas. Atlikus vienuoliktąją<br />

fotolitografiją bei suformavus KMOP tranzistorių<br />

TiSi 2<br />

ominius kontaktus, jau galima modeliuoti ir elektrines charakteristikas.<br />

Apačioje pateiktas programinis kodas, naudotinas<br />

elektrinėms charakteristikoms modeliuoti:<br />

# Pasirenkama Athena modeliavimo programa<br />

go athena<br />

# Gautas vaizdas po vienuoliktosios fotolitografijos<br />

init infile=lithography_11.str<br />

112