mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

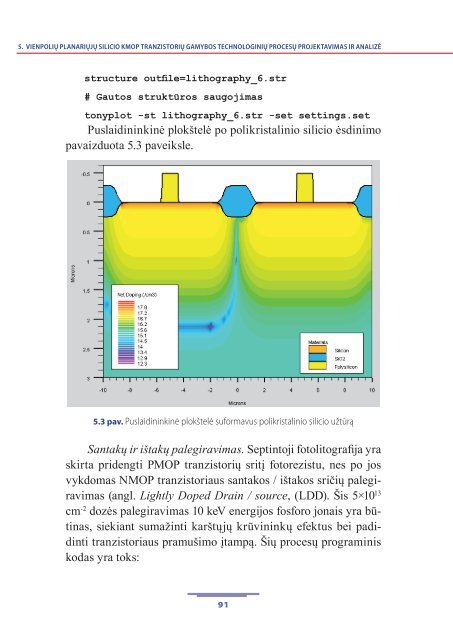

5. VIENPOLIŲ PLANARIŲJŲ SILICIO KMOP TRANZISTORIŲ GAMYBOS TECHNOLOGINIŲ PROCESŲ PROJEKTAVIMAS IR ANALIZĖ<br />

structure outfile=lithography_6.str<br />

# Gautos struktūros saugojimas<br />

tonyplot -st lithography_6.str -set settings.set<br />

Puslaidininkinė plokštelė po polikristalinio silicio ėsdinimo<br />

pavaizduota 5.3 paveiksle.<br />

5.3 pav. Puslaidininkinė plokštelė suformavus polikristalinio silicio užtūrą<br />

Santakų ir ištakų palegiravimas. Septintoji fotolitografija yra<br />

skirta pridengti PMOP tranzistorių sritį fotorezistu, nes po jos<br />

vykdomas NMOP tranzistoriaus santakos / ištakos sričių palegiravimas<br />

(angl. Lightly Doped Drain / source, (LDD). Šis 5×10 13<br />

cm -2 dozės palegiravimas 10 keV energijos fosforo jonais yra būtinas,<br />

siekiant sumažinti karštųjų krūvininkų efektus bei padidinti<br />

tranzistoriaus pramušimo įtampą. Šių procesų programinis<br />

kodas yra toks:<br />

91