mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

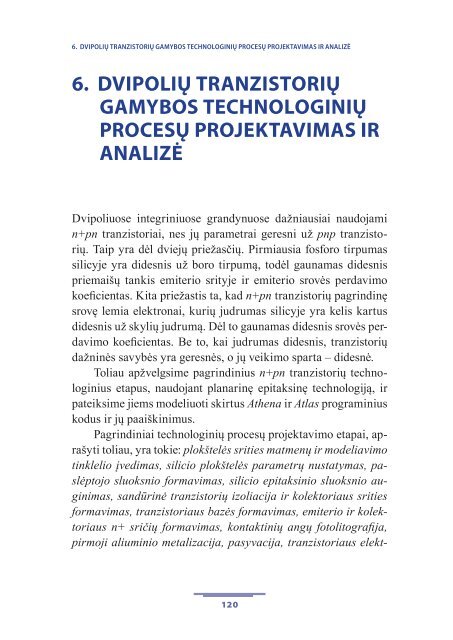

6. DVIPOLIŲ TRANZISTORIŲ GAMYBOS TECHNOLOGINIŲ PROCESŲ PROJEKTAVIMAS IR ANALIZĖ<br />

6. Dvipolių tranzistorių<br />

gamybos technologinių<br />

procesų projektavimas ir<br />

analizė<br />

Dvipoliuose integriniuose grandynuose dažniausiai naudojami<br />

n+pn tranzistoriai, nes jų parametrai geresni už pnp tranzistorių.<br />

Taip yra dėl dviejų priežasčių. Pirmiausia fosforo tirpumas<br />

silicyje yra didesnis už boro tirpumą, todėl gaunamas didesnis<br />

priemaišų tankis emiterio srityje ir emiterio srovės perdavimo<br />

koeficientas. Kita priežastis ta, kad n+pn tranzistorių pagrindinę<br />

srovę lemia elektronai, kurių judrumas silicyje yra kelis kartus<br />

didesnis už skylių judrumą. Dėl to gaunamas didesnis srovės perdavimo<br />

koeficientas. Be to, kai judrumas didesnis, tranzistorių<br />

dažninės savybės yra geresnės, o jų veikimo sparta – didesnė.<br />

Toliau apžvelgsime pagrindinius n+pn tranzistorių technologinius<br />

etapus, naudojant planarinę epitaksinę technologiją, ir<br />

pateiksime jiems modeliuoti skirtus Athena ir Atlas programinius<br />

kodus ir jų paaiškinimus.<br />

Pagrindiniai technologinių procesų projektavimo etapai, aprašyti<br />

toliau, yra tokie: plokštelės srities matmenų ir modeliavimo<br />

tinklelio įvedimas, silicio plokštelės parametrų nustatymas, paslėptojo<br />

sluoksnio formavimas, silicio epitaksinio sluoksnio auginimas,<br />

sandūrinė tranzistorių izoliacija ir kolektoriaus srities<br />

formavimas, tranzistoriaus bazės formavimas, emiterio ir kolektoriaus<br />

n+ sričių formavimas, kontaktinių angų fotolitografija,<br />

pirmoji aliuminio metalizacija, pasyvacija, tranzistoriaus elekt-<br />

120