mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

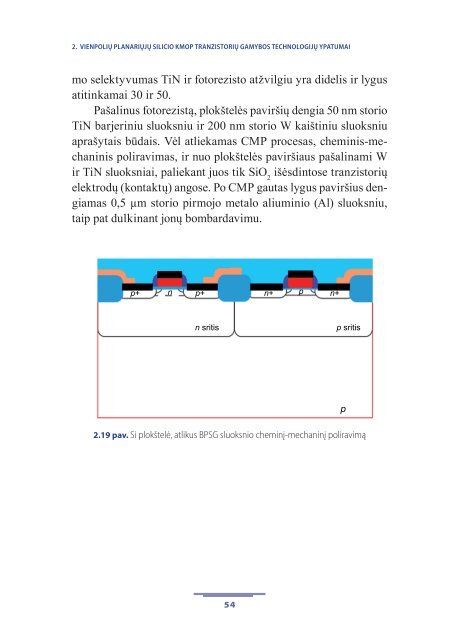

2. VIENPOLIŲ PLANARIŲJŲ SILICIO KMOP TRANZISTORIŲ GAMYBOS TECHNOLOGIJŲ YPATUMAI<br />

mo selektyvumas TiN ir fotorezisto atžvilgiu yra didelis ir lygus<br />

atitinkamai 30 ir 50.<br />

Pašalinus fotorezistą, plokštelės paviršių dengia 50 nm storio<br />

TiN barjeriniu sluoksniu ir 200 nm storio W kaištiniu sluoksniu<br />

aprašytais būdais. Vėl atliekamas CMP procesas, cheminis-mechaninis<br />

poliravimas, ir nuo plokštelės paviršiaus pašalinami W<br />

ir TiN sluoksniai, paliekant juos tik SiO 2<br />

išėsdintose tranzistorių<br />

elektrodų (kontaktų) angose. Po CMP gautas lygus paviršius dengiamas<br />

0,5 µm storio pirmojo metalo aliuminio (Al) sluoksniu,<br />

taip pat dulkinant jonų bombardavimu.<br />

n p<br />

p+ p+ n+ n+<br />

n sritis p sritis<br />

2.19 pav. Si plokštelė, atlikus BPSG sluoksnio cheminį-mechaninį poliravimą<br />

p<br />

54