mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

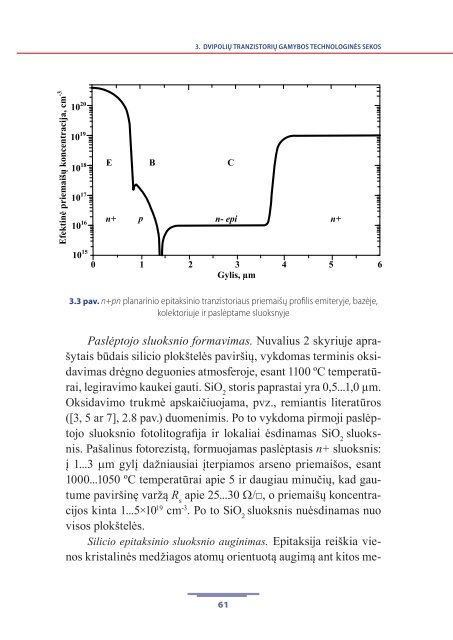

3. DVIPOLIŲ TRANZISTORIŲ GAMYBOS TECHNOLOGINĖS SEKOS<br />

Efektinė priemaišų koncentracija, cm -3<br />

10 20<br />

10 19<br />

10 18<br />

10 17<br />

10 16<br />

10 15<br />

E<br />

B<br />

n+ p n- epi<br />

n+<br />

C<br />

0 1 2 3 4 5 6<br />

Gylis, µm<br />

3.3 pav. n+pn planarinio epitaksinio tranzistoriaus priemaišų profilis emiteryje, bazėje,<br />

kolektoriuje ir paslėptame sluoksnyje<br />

Paslėptojo sluoksnio formavimas. Nuvalius 2 skyriuje aprašytais<br />

būdais silicio plokštelės paviršių, vykdomas terminis oksidavimas<br />

drėgno deguonies atmosferoje, esant 1100 ºC temperatūrai,<br />

legiravimo kaukei gauti. SiO 2<br />

storis paprastai yra 0,5...1,0 µm.<br />

Oksidavimo trukmė apskaičiuojama, pvz., remiantis literatūros<br />

([3, 5 ar 7], 2.8 pav.) duomenimis. Po to vykdoma pirmoji paslėptojo<br />

sluoksnio fotolitografija ir lokaliai ėsdinamas SiO 2<br />

sluoksnis.<br />

Pašalinus fotorezistą, formuojamas paslėptasis n+ sluoksnis:<br />

į 1...3 mm gylį dažniausiai įterpiamos arseno priemaišos, esant<br />

1000...1050 ºC temperatūrai apie 5 ir daugiau minučių, kad gautume<br />

paviršinę varžą R s<br />

apie 25...30 W/□, o priemaišų koncentracijos<br />

kinta 1...5×10 19 cm -3 . Po to SiO 2<br />

sluoksnis nuėsdinamas nuo<br />

visos plokštelės.<br />

Silicio epitaksinio sluoksnio auginimas. Epitaksija reiškia vienos<br />

kristalinės medžiagos atomų orientuotą augimą ant kitos me-<br />

61