mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

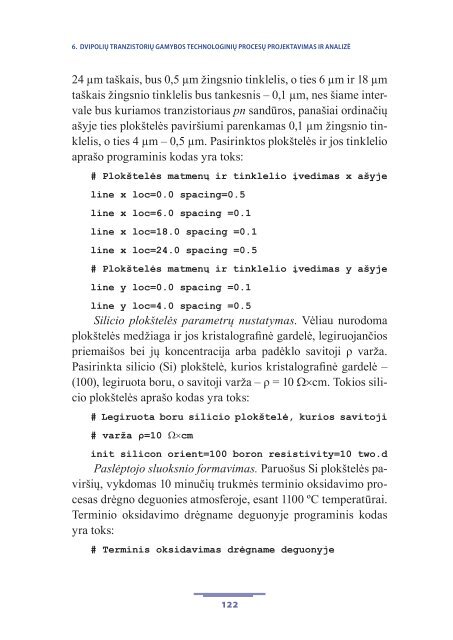

6. DVIPOLIŲ TRANZISTORIŲ GAMYBOS TECHNOLOGINIŲ PROCESŲ PROJEKTAVIMAS IR ANALIZĖ<br />

24 µm taškais, bus 0,5 µm žingsnio tinklelis, o ties 6 µm ir 18 µm<br />

taškais žingsnio tinklelis bus tankesnis – 0,1 µm, nes šiame intervale<br />

bus kuriamos tranzistoriaus pn sandūros, panašiai ordinačių<br />

ašyje ties plokštelės paviršiumi parenkamas 0,1 µm žingsnio tinklelis,<br />

o ties 4 µm – 0,5 µm. Pasirinktos plokštelės ir jos tinklelio<br />

aprašo programinis kodas yra toks:<br />

# Plokštelės matmenų ir tinklelio įvedimas x ašyje<br />

line x loc=0.0 spacing=0.5<br />

line x loc=6.0 spacing =0.1<br />

line x loc=18.0 spacing =0.1<br />

line x loc=24.0 spacing =0.5<br />

# Plokštelės matmenų ir tinklelio įvedimas y ašyje<br />

line y loc=0.0 spacing =0.1<br />

line y loc=4.0 spacing =0.5<br />

Silicio plokštelės parametrų nustatymas. Vėliau nurodoma<br />

plokštelės medžiaga ir jos kristalografinė gardelė, legiruojančios<br />

priemaišos bei jų koncentracija arba padėklo savitoji ρ varža.<br />

Pasirinkta silicio (Si) plokštelė, kurios kristalografinė gardelė –<br />

(100), legiruota boru, o savitoji varža – ρ = 10 W×cm. Tokios silicio<br />

plokštelės aprašo kodas yra toks:<br />

# Legiruota boru silicio plokštelė, kurios savitoji<br />

# varža ρ=10 W×cm<br />

init silicon orient=100 boron resistivity=10 two.d<br />

Paslėptojo sluoksnio formavimas. Paruošus Si plokštelės paviršių,<br />

vykdomas 10 minučių trukmės terminio oksidavimo procesas<br />

drėgno deguonies atmosferoje, esant 1100 ºC temperatūrai.<br />

Terminio oksidavimo drėgname deguonyje programinis kodas<br />

yra toks:<br />

# Terminis oksidavimas drėgname deguonyje<br />

122