mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

mikroschemų technologijų analizė - Vilniaus Gedimino technikos ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

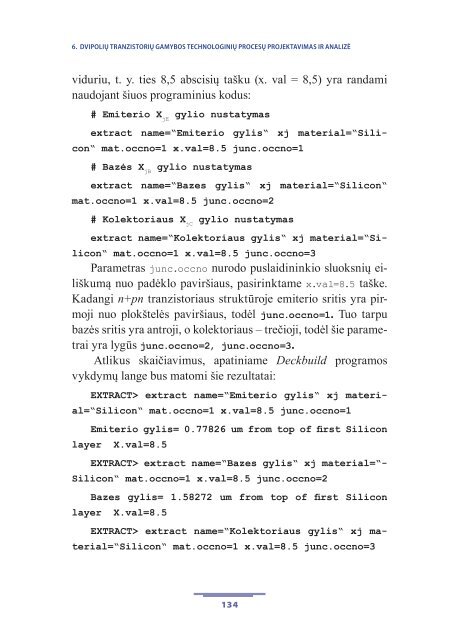

6. DVIPOLIŲ TRANZISTORIŲ GAMYBOS TECHNOLOGINIŲ PROCESŲ PROJEKTAVIMAS IR ANALIZĖ<br />

viduriu, t. y. ties 8,5 abscisių tašku (x. val = 8,5) yra randami<br />

naudojant šiuos programinius kodus:<br />

# Emiterio X jE<br />

gylio nustatymas<br />

extract name=“Emiterio gylis“ xj material=“Silicon“<br />

mat.occno=1 x.val=8.5 junc.occno=1<br />

# Bazės X jB<br />

gylio nustatymas<br />

extract name=“Bazes gylis“ xj material=“Silicon“<br />

mat.occno=1 x.val=8.5 junc.occno=2<br />

# Kolektoriaus X jC<br />

gylio nustatymas<br />

extract name=“Kolektoriaus gylis“ xj material=“Silicon“<br />

mat.occno=1 x.val=8.5 junc.occno=3<br />

Parametras junc.occno nurodo puslaidininkio sluoksnių eiliškumą<br />

nuo padėklo paviršiaus, pasirinktame x.val=8.5 taške.<br />

Kadangi n+pn tranzistoriaus struktūroje emiterio sritis yra pirmoji<br />

nuo plokštelės paviršiaus, todėl junc.occno=1. Tuo tarpu<br />

bazės sritis yra antroji, o kolektoriaus – trečioji, todėl šie parametrai<br />

yra lygūs junc.occno=2, junc.occno=3.<br />

Atlikus skaičiavimus, apatiniame Deckbuild programos<br />

vykdymų lange bus matomi šie rezultatai:<br />

EXTRACT> extract name=“Emiterio gylis“ xj material=“Silicon“<br />

mat.occno=1 x.val=8.5 junc.occno=1<br />

Emiterio gylis= 0.77826 um from top of first Silicon<br />

layer X.val=8.5<br />

EXTRACT> extract name=“Bazes gylis“ xj material=“-<br />

Silicon“ mat.occno=1 x.val=8.5 junc.occno=2<br />

Bazes gylis= 1.58272 um from top of first Silicon<br />

layer X.val=8.5<br />

EXTRACT> extract name=“Kolektoriaus gylis“ xj material=“Silicon“<br />

mat.occno=1 x.val=8.5 junc.occno=3<br />

134