DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

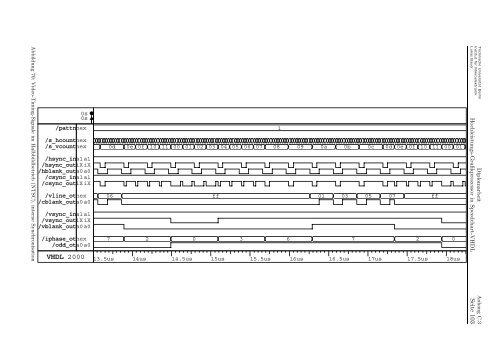

Abbildung 70: Video-Timing-Signale im Halbbildbetrieb (NTSC), interne Synchronisation<br />

0s<br />

0s<br />

/pattn /pattnhex<br />

/s_hcount<br />

/s_hcounthex<br />

/s_vcount<br />

/s_vcounthex<br />

/hsync_in<br />

/hsync_ina1<br />

a1<br />

/hsync_out<br />

/hsync_outiX<br />

iX<br />

/hblank_out<br />

/hblank_outa0<br />

a0<br />

/csync_in<br />

/csync_ina1<br />

a1<br />

/csync_out<br />

/csync_outiX<br />

iX<br />

/vline_ot<br />

/vline_othex<br />

/cblank_out<br />

/cblank_outa0<br />

a0<br />

/vsync_in<br />

/vsync_ina1<br />

a1<br />

/vsync_out<br />

/vsync_outiX<br />

iX<br />

/vblank_out<br />

/vblank_outa0<br />

a0<br />

/iphase_ot<br />

/iphase_othex<br />

/odd_ot /odd_ota0<br />

a0<br />

VHDL 2000<br />

1<br />

0d 0e 0f 10 11 00 01 02 03 04 05 06 07 08 09 0a 0b 0c 0d 0e 0f 10 11 00 01<br />

06 ff 01 03 05 07 ff<br />

7 2 0 3 6 7 2 0<br />

13.5us 14us 14.5us 15us 15.5us 16us 16.5us 17us 17.5us 18us<br />

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Anhang C.3<br />

Seite 103