DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

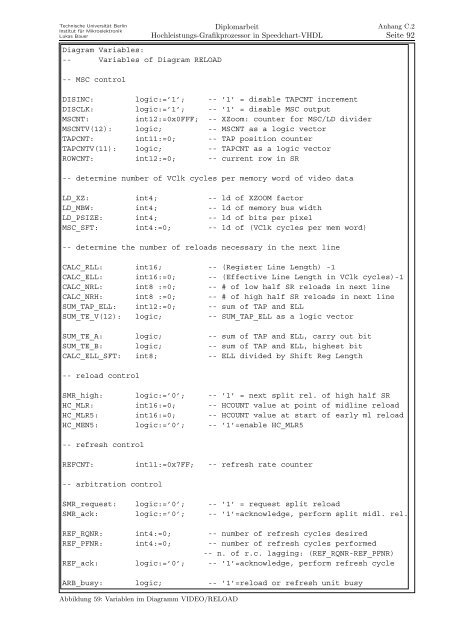

Diagram Variables:<br />

-- Variables of Diagram RELOAD<br />

-- MSC control<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

DISINC: logic:=’1’; -- ’1’ = disable TAPCNT increment<br />

DISCLK: logic:=’1’; -- ’1’ = disable MSC output<br />

MSCNT: int12:=0x0FFF; -- XZoom: counter for MSC/LD divider<br />

MSCNTV(12): logic; -- MSCNT as a logic vector<br />

TAPCNT: int11:=0; -- TAP position counter<br />

TAPCNTV(11): logic; -- TAPCNT as a logic vector<br />

ROWCNT: int12:=0; -- current row in SR<br />

-- determine number of VClk cycles per memory word of video data<br />

LD_XZ: int4; -- ld of XZOOM factor<br />

LD_MBW: int4; -- ld of memory bus width<br />

LD_PSIZE: int4; -- ld of bits per pixel<br />

MSC_SFT: int4:=0; -- ld of (VClk cycles per mem word)<br />

-- determine the number of reloads necessary in the next line<br />

Anhang C.2<br />

Seite 92<br />

CALC_RLL: int16; -- (Register Line Length) -1<br />

CALC_ELL: int16:=0; -- (Effective Line Length in VClk cycles)-1<br />

CALC_NRL: int8 :=0; -- # of low half SR reloads in next line<br />

CALC_NRH: int8 :=0; -- # of high half SR reloads in next line<br />

SUM_TAP_ELL: int12:=0; -- sum of TAP and ELL<br />

SUM_TE_V(12): logic; -- SUM_TAP_ELL as a logic vector<br />

SUM_TE_A: logic; -- sum of TAP and ELL, carry out bit<br />

SUM_TE_B: logic; -- sum of TAP and ELL, highest bit<br />

CALC_ELL_SFT: int8; -- ELL divided by Shift Reg Length<br />

-- reload control<br />

SMR_high: logic:=’0’; -- ’1’ = next split rel. of high half SR<br />

HC_MLR: int16:=0; -- HCOUNT value at point of midline reload<br />

HC_MLR5: int16:=0; -- HCOUNT value at start of early ml reload<br />

HC_MEN5: logic:=’0’; -- ’1’=enable HC_MLR5<br />

-- refresh control<br />

REFCNT: int11:=0x7FF; -- refresh rate counter<br />

-- arbitration control<br />

SMR_request: logic:=’0’; -- ’1’ = request split reload<br />

SMR_ack: logic:=’0’; -- ’1’=acknowledge, perform split midl. rel.<br />

REF_RQNR: int4:=0; -- number of refresh cycles desired<br />

REF_PFNR: int4:=0; -- number of refresh cycles performed<br />

-- n. of r.c. lagging: (REF_RQNR-REF_PFNR)<br />

REF_ack: logic:=’0’; -- ’1’=acknowledge, perform refresh cycle<br />

ARB_busy: logic; -- ’1’=reload or refresh unit busy<br />

Abbildung 59: Variablen im Diagramm VIDEO/RELOAD