DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

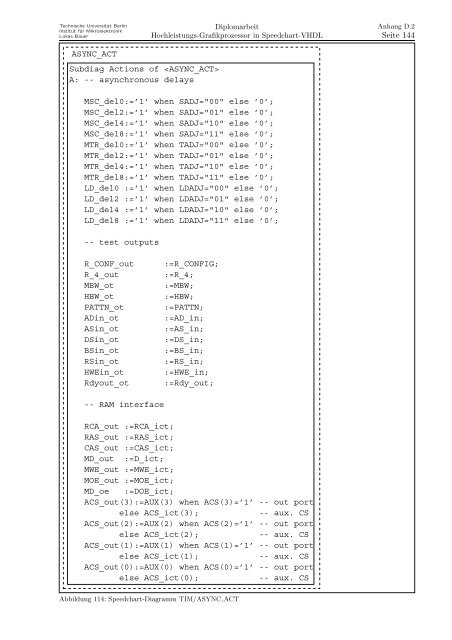

ASYNC_ACT<br />

Subdiag Actions of <br />

A: -- asynchronous delays<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

MSC_del0:=’1’ when SADJ="00" else ’0’;<br />

MSC_del2:=’1’ when SADJ="01" else ’0’;<br />

MSC_del4:=’1’ when SADJ="10" else ’0’;<br />

MSC_del8:=’1’ when SADJ="11" else ’0’;<br />

MTR_del0:=’1’ when TADJ="00" else ’0’;<br />

MTR_del2:=’1’ when TADJ="01" else ’0’;<br />

MTR_del4:=’1’ when TADJ="10" else ’0’;<br />

MTR_del8:=’1’ when TADJ="11" else ’0’;<br />

LD_del0 :=’1’ when LDADJ="00" else ’0’;<br />

LD_del2 :=’1’ when LDADJ="01" else ’0’;<br />

LD_del4 :=’1’ when LDADJ="10" else ’0’;<br />

LD_del8 :=’1’ when LDADJ="11" else ’0’;<br />

-- test outputs<br />

R_CONF_out :=R_CONFIG;<br />

R_4_out :=R_4;<br />

MBW_ot :=MBW;<br />

HBW_ot :=HBW;<br />

PATTN_ot :=PATTN;<br />

ADin_ot :=AD_in;<br />

ASin_ot :=AS_in;<br />

DSin_ot :=DS_in;<br />

BSin_ot :=BS_in;<br />

RSin_ot :=RS_in;<br />

HWEin_ot :=HWE_in;<br />

Rdyout_ot :=Rdy_out;<br />

-- RAM interface<br />

RCA_out :=RCA_ict;<br />

RAS_out :=RAS_ict;<br />

CAS_out :=CAS_ict;<br />

MD_out :=D_ict;<br />

MWE_out :=MWE_ict;<br />

MOE_out :=MOE_ict;<br />

MD_oe :=DOE_ict;<br />

ACS_out(3):=AUX(3) when ACS(3)=’1’ -- out port<br />

else ACS_ict(3); -- aux. CS<br />

ACS_out(2):=AUX(2) when ACS(2)=’1’ -- out port<br />

else ACS_ict(2); -- aux. CS<br />

ACS_out(1):=AUX(1) when ACS(1)=’1’ -- out port<br />

else ACS_ict(1); -- aux. CS<br />

ACS_out(0):=AUX(0) when ACS(0)=’1’ -- out port<br />

else ACS_ict(0); -- aux. CS<br />

Abbildung 114: Speedchart-Diagramm TIM/ASYNC ACT<br />

Anhang D.2<br />

Seite 144