DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Übersicht über die externen Signale<br />

Anhang A.2<br />

Seite 69<br />

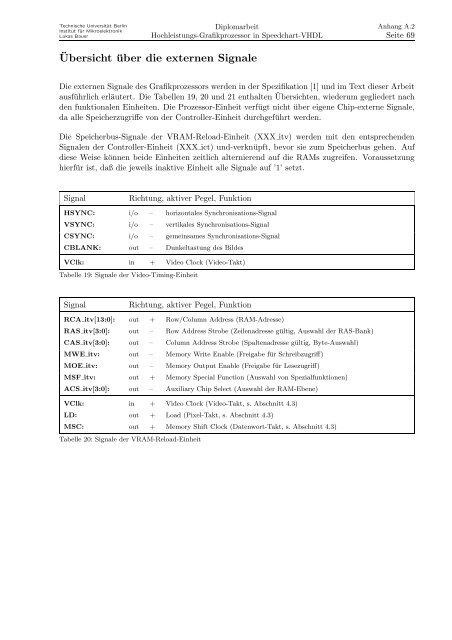

Die externen Signale des Grafikprozessors werden in der Spezifikation [1] und im Text dieser Arbeit<br />

ausführlich erläutert. Die Tabellen 19, 20 und 21 enthalten Übersichten, wiederum gegliedert nach<br />

den funktionalen Einheiten. Die Prozessor-Einheit verfügt nicht über eigene Chip-externe Signale,<br />

da alle Speicherzugriffe von der Controller-Einheit durchgeführt werden.<br />

Die Speicherbus-Signale der VRAM-Reload-Einheit (XXX itv) werden mit den entsprechenden<br />

Signalen der Controller-Einheit (XXX ict) und-verknüpft, bevor sie zum Speicherbus gehen. Auf<br />

diese Weise können beide Einheiten zeitlich alternierend auf die RAMs zugreifen. Voraussetzung<br />

hierfür ist, daß die jeweils inaktive Einheit alle Signale auf ’1’ setzt.<br />

Signal Richtung, aktiver Pegel, Funktion<br />

HSYNC: i/o – horizontales Synchronisations-Signal<br />

VSYNC: i/o – vertikales Synchronisations-Signal<br />

CSYNC: i/o – gemeinsames Synchronisations-Signal<br />

CBLANK: out – Dunkeltastung des Bildes<br />

VClk: in + Video Clock (Video-Takt)<br />

Tabelle 19: Signale der Video-Timing-Einheit<br />

Signal Richtung, aktiver Pegel, Funktion<br />

RCA itv[13:0]: out + Row/Column Address (RAM-Adresse)<br />

RAS itv[3:0]: out – Row Address Strobe (Zeilenadresse gültig, Auswahl der RAS-Bank)<br />

CAS itv[3:0]: out – Column Address Strobe (Spaltenadresse gültig, Byte-Auswahl)<br />

MWE itv: out – Memory Write Enable (Freigabe für Schreibzugriff)<br />

MOE itv: out – Memory Output Enable (Freigabe für Lesezugriff)<br />

MSF itv: out + Memory Special Function (Auswahl von Spezialfunktionen)<br />

ACS itv[3:0]: out – Auxiliary Chip Select (Auswahl der RAM-Ebene)<br />

VClk: in + Video Clock (Video-Takt, s. Abschnitt 4.3)<br />

LD: out + Load (Pixel-Takt, s. Abschnitt 4.3)<br />

MSC: out + Memory Shift Clock (Datenwort-Takt, s. Abschnitt 4.3)<br />

Tabelle 20: Signale der VRAM-Reload-Einheit