DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abschnitt 3.2<br />

Seite 15<br />

Vertikalzähler wurde daher beim TI-34020 so beschaltet, daß er in manchen Phasen des vertikalen<br />

Timings zweimal pro Zeile erhöht wird, was in Abbildung 10 zu sehen ist. Aus Kompatibilitätsgründen<br />

wurde das Verhalten des Zählers exakt vom TI-34020 übernommen.<br />

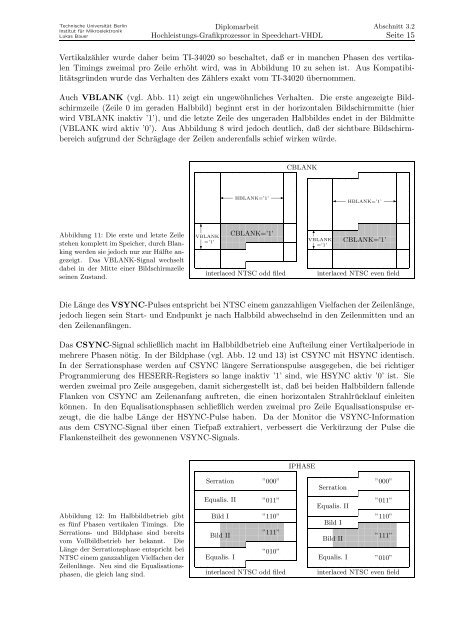

Auch VBLANK (vgl. Abb. 11) zeigt ein ungewöhnliches Verhalten. Die erste angezeigte Bildschirmzeile<br />

(Zeile 0 im geraden Halbbild) beginnt erst in der horizontalen Bildschirmmitte (hier<br />

wird VBLANK inaktiv ’1’), und die letzte Zeile des ungeraden Halbbildes endet in der Bildmitte<br />

(VBLANK wird aktiv ’0’). Aus Abbildung 8 wird jedoch deutlich, daß der sichtbare Bildschirmbereich<br />

aufgrund der Schräglage der Zeilen anderenfalls schief wirken würde.<br />

Abbildung 11: Die erste und letzte Zeile<br />

stehen komplett im Speicher, durch Blanking<br />

werden sie jedoch nur zur Hälfte angezeigt.<br />

Das VBLANK-Signal wechselt<br />

dabei in der Mitte einer Bildschirmzeile<br />

seinen Zustand.<br />

✻<br />

VBLANK<br />

=’1’<br />

❄<br />

✛ ✲<br />

HBLANK=’1’<br />

CBLANK=’1’<br />

interlaced NTSC odd filed<br />

CBLANK<br />

✻<br />

VBLANK<br />

=’1’<br />

❄<br />

✛ ✲<br />

HBLANK=’1’<br />

CBLANK=’1’<br />

interlaced NTSC even field<br />

Die Länge des VSYNC-Pulses entspricht bei NTSC einem ganzzahligen Vielfachen der Zeilenlänge,<br />

jedoch liegen sein Start- und Endpunkt je nach Halbbild abwechselnd in den Zeilenmitten und an<br />

den Zeilenanfängen.<br />

Das CSYNC-Signal schließlich macht im Halbbildbetrieb eine Aufteilung einer Vertikalperiode in<br />

mehrere Phasen nötig. In der Bildphase (vgl. Abb. 12 und 13) ist CSYNC mit HSYNC identisch.<br />

In der Serrationsphase werden auf CSYNC längere Serrationspulse ausgegeben, die bei richtiger<br />

Programmierung des HESERR-Registers so lange inaktiv ’1’ sind, wie HSYNC aktiv ’0’ ist. Sie<br />

werden zweimal pro Zeile ausgegeben, damit sichergestellt ist, daß bei beiden Halbbildern fallende<br />

Flanken von CSYNC am Zeilenanfang auftreten, die einen horizontalen Strahlrücklauf einleiten<br />

können. In den Equalisationsphasen schließlich werden zweimal pro Zeile Equalisationspulse erzeugt,<br />

die die halbe Länge der HSYNC-Pulse haben. Da der Monitor die VSYNC-Information<br />

aus dem CSYNC-Signal über einen Tiefpaß extrahiert, verbessert die Verkürzung der Pulse die<br />

Flankensteilheit des gewonnenen VSYNC-Signals.<br />

Abbildung 12: Im Halbbildbetrieb gibt<br />

es fünf Phasen vertikalen Timings. Die<br />

Serrations- und Bildphase sind bereits<br />

vom Vollbildbetrieb her bekannt. Die<br />

Länge der Serrationsphase entspricht bei<br />

NTSC einem ganzzahligen Vielfachen der<br />

Zeilenlänge. Neu sind die Equalisationsphasen,<br />

die gleich lang sind.<br />

Serration ”000”<br />

Equalis. II ”011”<br />

Bild I ”110”<br />

Bild II<br />

Equalis. I<br />

”111”<br />

”010”<br />

interlaced NTSC odd filed<br />

IPHASE<br />

Serration<br />

Equalis. II<br />

Bild I<br />

Bild II<br />

”000”<br />

”011”<br />

”110”<br />

”111”<br />

Equalis. I ”010”<br />

interlaced NTSC even field