DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

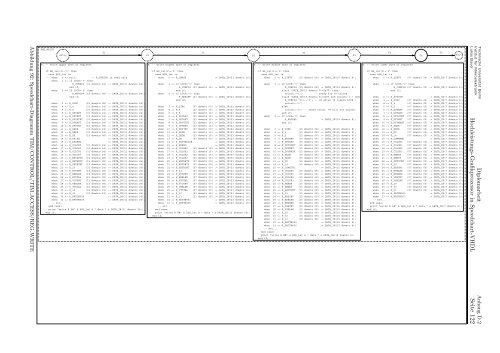

Abbildung 92: Speedchart-Diagramm TIM/CONTROL/TIM ACCESS/REG WRITE<br />

REG_WRITE<br />

entry<br />

T1 T2 T3 T4 T5<br />

S1<br />

S2<br />

S3<br />

S4<br />

A: -- write upper byte of register<br />

A: -- write higher byte of register<br />

A: -- write middle byte of register<br />

A: -- write lower byte of register<br />

if BS_lat(3)=’0’ then<br />

if BS_lat(2)=’0’ then<br />

if BS_lat(1)=’0’ then<br />

if BS_lat(0)=’0’ then<br />

case ADS_lat is<br />

case ADS_lat is<br />

case ADS_lat is<br />

case ADS_lat is<br />

-- when 0 => null; -- R_STA<strong>TU</strong>S is read only<br />

when 1 => if LOCK=’0’ then<br />

when 0 => R_IMASK := DATA_IN(23 downto 16);<br />

when 0 => R_LINTV (15 downto 08) := DATA_IN(15 downto 8);<br />

when 0 => R_LINTV (07 downto 00) := DATA_IN(7 downto 0);<br />

R_CONFIG (31 downto 24) := DATA_IN(31 downto 24);<br />

when 1 => if LOCK=’0’ then<br />

when 1 => if LOCK=’0’ then<br />

when 1 => if LOCK=’0’ then<br />

end if;<br />

R_CONFIG (23 downto 16) := DATA_IN(23 downto 16);<br />

R_CONFIG (15 downto 08) := DATA_IN(15 downto 8);<br />

R_CONFIG (07 downto 00) := DATA_IN(7 downto 0);<br />

when 2 => if LOCK=’0’ then<br />

end if;<br />

elsif (DATA_IN(15 downto 8)=0x7F) then<br />

end if;<br />

R_MUXOFF (15 downto 08) := DATA_IN(31 downto 24);<br />

when 2 => if LOCK=’0’ then<br />

unlock:=’1’; -- ready for 7F-unlock<br />

end if;<br />

R_MUXOFF (07 downto 00) := DATA_IN(23 downto 16);<br />

elsif (DATA_IN(15 downto 8)=0x55 and unlock=’1’) then when 2 => R_XYZOOM := DATA_IN(7 downto 0);<br />

end if;<br />

R_CONFIG (15):=’0’; -- 55 after 7F clears LOCK !<br />

when 3 => R_DINC (07 downto 00) := DATA_IN(7 downto 0);<br />

when 3 => R_SINC (15 downto 08) := DATA_IN(31 downto 24);<br />

unlock:=’0’;<br />

when 4 => R_4 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 4 => R_4 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 3 => R_SINC (07 downto 00) := DATA_IN(23 downto 16);<br />

else<br />

when 5 => R_5 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 5 => R_5 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 4 => R_4 (23 downto 16) := DATA_IN(23 downto 16);<br />

unlock:=’0’; -- other value, 7F will not unlock.<br />

when 6 => R_SSTART (07 downto 00) := DATA_IN(7 downto 0);<br />

when 6 => R_SSTART (31 downto 24) := DATA_IN(31 downto 24);<br />

when 5 => R_5 (23 downto 16) := DATA_IN(23 downto 16);<br />

end if;<br />

when 7 => R_DSTART (07 downto 00) := DATA_IN(7 downto 0);<br />

when 7 => R_DSTART (31 downto 24) := DATA_IN(31 downto 24);<br />

when 6 => R_SSTART (23 downto 16) := DATA_IN(23 downto 16);<br />

when 2 => if LOCK=’0’ then<br />

when 8 => R_DPYSTRT (07 downto 00) := DATA_IN(7 downto 0);<br />

when 8 => R_DPYSTRT (31 downto 24) := DATA_IN(31 downto 24);<br />

when 7 => R_DSTART (23 downto 16) := DATA_IN(23 downto 16);<br />

R_RADSEL := DATA_IN(15 downto 8);<br />

when 9 => R_DPYNXT (07 downto 00) := DATA_IN(7 downto 0);<br />

when 9 => R_DPYNXT (31 downto 24) := DATA_IN(31 downto 24);<br />

when 8 => R_DPYSTRT (23 downto 16) := DATA_IN(23 downto 16);<br />

end if;<br />

when 10 => R_DPYMASK (07 downto 00) := DATA_IN(7 downto 0);<br />

when 10 => R_DPYINC (15 downto 08) := DATA_IN(31 downto 24);<br />

when 9 => R_DPYNXT (23 downto 16) := DATA_IN(23 downto 16);<br />

when 11 => R_SADR (07 downto 00) := DATA_IN(7 downto 0);<br />

when 11 => R_SADR (31 downto 24) := DATA_IN(31 downto 24);<br />

when 10 => R_DPYINC (07 downto 00) := DATA_IN(23 downto 16);<br />

when 3 => R_DINC (15 downto 08) := DATA_IN(15 downto 8);<br />

when 12 => R_DADR (07 downto 00) := DATA_IN(7 downto 0);<br />

when 12 => R_DADR (31 downto 24) := DATA_IN(31 downto 24);<br />

when 11 => R_SADR (23 downto 16) := DATA_IN(23 downto 16);<br />

when 4 => R_4 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 13 => R_DY (07 downto 00) := DATA_IN(7 downto 0);<br />

when 13 => R_DX (15 downto 08) := DATA_IN(31 downto 24);<br />

when 12 => R_DADR (23 downto 16) := DATA_IN(23 downto 16);<br />

when 5 => R_5 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 14 => R_14 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 14 => R_PSIZE := DATA_IN(31 downto 24);<br />

when 13 => R_DX (07 downto 00) := DATA_IN(23 downto 16);<br />

when 6 => R_SSTART (15 downto 08) := DATA_IN(15 downto 8);<br />

when 15 => R_COMMAND := DATA_IN(7 downto 0);<br />

when 15 => R_AUXREG := DATA_IN(31 downto 24);<br />

when 14 => R_PATTNSIZE := DATA_IN(23 downto 16);<br />

when 7 => R_DSTART (15 downto 08) := DATA_IN(15 downto 8);<br />

when 16 => R_COLOR0 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 16 => R_COLOR0 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 15 => R_HDREG := DATA_IN(23 downto 16);<br />

when 8 => R_DPYSTRT (15 downto 08) := DATA_IN(15 downto 8);<br />

when 17 => R_COLOR1 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 17 => R_COLOR1 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 16 => R_COLOR0 (23 downto 16) := DATA_IN(23 downto 16);<br />

when 9 => R_DPYNXT (15 downto 08) := DATA_IN(15 downto 8);<br />

when 18 => R_COLOR2 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 18 => R_COLOR2 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 17 => R_COLOR1 (23 downto 16) := DATA_IN(23 downto 16);<br />

when 10 => R_DPYMASK (15 downto 08) := DATA_IN(15 downto 8);<br />

when 19 => R_COLOR3 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 19 => R_COLOR3 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 18 => R_COLOR2 (23 downto 16) := DATA_IN(23 downto 16);<br />

when 11 => R_SADR (15 downto 08) := DATA_IN(15 downto 8);<br />

when 20 => R_WENDX (07 downto 00) := DATA_IN(7 downto 0);<br />

when 20 => R_WSTARTX (15 downto 08) := DATA_IN(31 downto 24);<br />

when 19 => R_COLOR3 (23 downto 16) := DATA_IN(23 downto 16);<br />

when 12 => R_DADR (15 downto 08) := DATA_IN(15 downto 8);<br />

when 21 => R_WENDY (07 downto 00) := DATA_IN(7 downto 0);<br />

when 21 => R_WSTARTY (15 downto 08) := DATA_IN(31 downto 24);<br />

when 20 => R_WSTARTX (07 downto 00) := DATA_IN(23 downto 16);<br />

when 13 => R_DY (15 downto 08) := DATA_IN(15 downto 8);<br />

when 22 => R_SETVCNT (07 downto 00) := DATA_IN(7 downto 0);<br />

when 22 => R_SETHCNT (15 downto 08) := DATA_IN(31 downto 24);<br />

when 21 => R_WSTARTY (07 downto 00) := DATA_IN(23 downto 16);<br />

when 14 => R_14 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 23 => R_23 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 23 => R_23 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 22 => R_SETHCNT (07 downto 00) := DATA_IN(23 downto 16);<br />

when 15 => R_COMCTRL := DATA_IN(15 downto 8);<br />

when 24 => R_HESYNC (07 downto 00) := DATA_IN(7 downto 0);<br />

when 24 => R_HCOUNT (15 downto 08) := DATA_IN(31 downto 24);<br />

when 23 => R_23 (23 downto 16) := DATA_IN(23 downto 16);<br />

when 16 => R_COLOR0 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 25 => R_HSBLNK (07 downto 00) := DATA_IN(7 downto 0);<br />

when 25 => R_HEBLNK (15 downto 08) := DATA_IN(31 downto 24);<br />

when 24 => R_HCOUNT (07 downto 00) := DATA_IN(23 downto 16);<br />

when 17 => R_COLOR1 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 26 => R_HESERR (07 downto 00) := DATA_IN(7 downto 0);<br />

when 26 => R_HTOTAL (15 downto 08) := DATA_IN(31 downto 24);<br />

when 25 => R_HEBLNK (07 downto 00) := DATA_IN(23 downto 16);<br />

when 18 => R_COLOR2 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 27 => R_VESYNC (07 downto 00) := DATA_IN(7 downto 0);<br />

when 27 => R_VCOUNT (15 downto 08) := DATA_IN(31 downto 24);<br />

when 26 => R_HTOTAL (07 downto 00) := DATA_IN(23 downto 16);<br />

when 19 => R_COLOR3 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 28 => R_VSBLNK (07 downto 00) := DATA_IN(7 downto 0);<br />

when 28 => R_VEBLNK (15 downto 08) := DATA_IN(31 downto 24);<br />

when 27 => R_VCOUNT (07 downto 00) := DATA_IN(23 downto 16);<br />

when 20 => R_WENDX (15 downto 08) := DATA_IN(15 downto 8);<br />

when 29 => R_29 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 29 => R_VTOTAL (15 downto 08) := DATA_IN(31 downto 24);<br />

when 28 => R_VEBLNK (07 downto 00) := DATA_IN(23 downto 16);<br />

when 21 => R_WENDY (15 downto 08) := DATA_IN(15 downto 8);<br />

when 30 => R_30 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 30 => R_30 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 29 => R_VTOTAL (07 downto 00) := DATA_IN(23 downto 16);<br />

when 22 => R_SETVCNT (15 downto 08) := DATA_IN(15 downto 8);<br />

when 31 => R_31 (07 downto 00) := DATA_IN(7 downto 0);<br />

when 31 => R_31 (31 downto 24) := DATA_IN(31 downto 24);<br />

when 30 => R_30 (23 downto 16) := DATA_IN(23 downto 16);<br />

when 23 => R_23 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 32 => R_PATTN003 := DATA_IN(7 downto 0);<br />

when 32 => R_PATTN000 := DATA_IN(31 downto 24);<br />

when 31 => R_31 (23 downto 16) := DATA_IN(23 downto 16);<br />

when 24 => R_HESYNC (15 downto 08) := DATA_IN(15 downto 8);<br />

when 33 => R_PATTN007 := DATA_IN(7 downto 0);<br />

when 33 => R_PATTN004 := DATA_IN(31 downto 24);<br />

when 32 => R_PATTN001 := DATA_IN(23 downto 16);<br />

when 25 => R_HSBLNK (15 downto 08) := DATA_IN(15 downto 8);<br />

-- etc...<br />

-- etc...<br />

when 33 => R_PATTN005 := DATA_IN(23 downto 16);<br />

when 26 => R_HESERR (15 downto 08) := DATA_IN(15 downto 8);<br />

end case;<br />

end case;<br />

-- etc...<br />

when 27 => R_VESYNC (15 downto 08) := DATA_IN(15 downto 8);<br />

print "write R L#" & ADS_lat & " data " & DATA_IN(7 downto 0);<br />

print "write R U#" & ADS_lat & " data " & DATA_IN(31 downto 24); end case;<br />

when 28 => R_VSBLNK (15 downto 08) := DATA_IN(15 downto 8); end if;<br />

end if;<br />

print "write R H#" & ADS_lat & " data " & DATA_IN(23 downto 16);<br />

when 29 => R_29 (15 downto 08) := DATA_IN(15 downto 8);<br />

end if;<br />

when 30 => R_30 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 31 => R_31 (15 downto 08) := DATA_IN(15 downto 8);<br />

when 32 => R_PATTN002 := DATA_IN(15 downto 8);<br />

when 33 => R_PATTN006 := DATA_IN(15 downto 8);<br />

-- etc...<br />

end case;<br />

print "write R M#" & ADS_lat & " data " & DATA_IN(15 downto 8);<br />

end if;<br />

exit<br />

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Anhang D.2<br />

Seite 122