DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

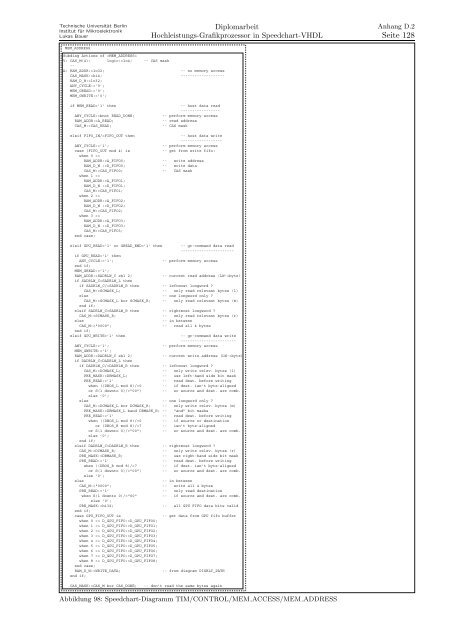

MEM_ADDRESS<br />

Subdiag Actions of <br />

V: CAS_M(4): logic:=lo4; -- CAS mask<br />

--<br />

A: RAM_ADDR:=lo32; -- no memory access<br />

CAS_MASK:=hi4; -------------------<br />

RAM_D_W:=lo32;<br />

ANY_CYCLE:=’0’;<br />

MEM_GREAD:=’0’;<br />

MEM_GWRITE:=’0’;<br />

if MEM_READ=’1’ then -- host data read<br />

-----------------<br />

ANY_CYCLE:=bnot READ_DONE; -- perform memory access<br />

RAM_ADDR:=A_READ; -- read address<br />

CAS_M:=CAS_READ; -- CAS mask<br />

elsif FIFO_IN/=FIFO_OUT then -- host data write<br />

------------------<br />

ANY_CYCLE:=’1’; -- perform memory access<br />

case (FIFO_OUT mod 4) is -- get from write fifo:<br />

when 0 =><br />

RAM_ADDR:=A_FIFO0; -- write address<br />

RAM_D_W :=D_FIFO0; -- write data<br />

CAS_M:=CAS_FIFO0; -- CAS mask<br />

when 1 =><br />

RAM_ADDR:=A_FIFO1;<br />

RAM_D_W :=D_FIFO1;<br />

CAS_M:=CAS_FIFO1;<br />

when 2 =><br />

RAM_ADDR:=A_FIFO2;<br />

RAM_D_W :=D_FIFO2;<br />

CAS_M:=CAS_FIFO2;<br />

when 3 =><br />

RAM_ADDR:=A_FIFO3;<br />

RAM_D_W :=D_FIFO3;<br />

CAS_M:=CAS_FIFO3;<br />

end case;<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

elsif GPU_READ=’1’ or GREAD_END=’1’ then -- gr-command data read<br />

----------------------if<br />

GPU_READ=’1’ then<br />

ANY_CYCLE:=’1’; -- perform memory access<br />

end if;<br />

MEM_GREAD:=’1’;<br />

RAM_ADDR:=SADRLW_C shl 2; -- current read address (LW->byte)<br />

if SADRLW_C=SADRLW_L then<br />

if SADRLW_C/=SADRLW_R then -- leftmost longword ?<br />

CAS_M:=SCMASK_L; -- only read relevant bytes (l)<br />

else -- one longword only ?<br />

CAS_M:=SCMASK_L bor SCMASK_R; -- only read relevant bytes (m)<br />

end if;<br />

elsif SADRLW_C=SADRLW_R then -- rightmost longword ?<br />

CAS_M:=SCMASK_R; -- only read relevant bytes (r)<br />

else -- in between<br />

CAS_M:="0000"; -- read all 4 bytes<br />

end if;<br />

elsif GPU_WRITE=’1’ then -- gr-command data write<br />

------------------------<br />

ANY_CYCLE:=’1’; -- perform memory access<br />

MEM_GWRITE:=’1’;<br />

RAM_ADDR:=DADRLW_C shl 2; -- current write address (LW->byte)<br />

if DADRLW_C=DADRLW_L then<br />

if DADRLW_C/=DADRLW_R then -- leftmost longword ?<br />

CAS_M:=DCMASK_L; -- only write relev. bytes (l)<br />

PRE_MASK:=DBMASK_L; -- use left-hand side bit mask<br />

PRE_READ:=’1’ -- read dest. before writing<br />

when ((DBOS_L mod 8)/=0 -- if dest. isn’t byte-aligned<br />

or S(1 downto 0)/="00") -- or source and dest. are comb.<br />

else ’0’;<br />

else -- one longword only ?<br />

CAS_M:=DCMASK_L bor DCMASK_R; -- only write relev. bytes (m)<br />

PRE_MASK:=DBMASK_L band DBMASK_R; -- "and" bit masks<br />

PRE_READ:=’1’ -- read dest. before writing<br />

when ((DBOS_L mod 8)/=0 -- if source or destination<br />

or (DBOS_R mod 8)/=7 -- isn’t byte-aligned<br />

or S(1 downto 0)/="00") -- or source and dest. are comb.<br />

else ’0’;<br />

end if;<br />

elsif DADRLW_C=DADRLW_R then -- rightmost longword ?<br />

CAS_M:=DCMASK_R; -- only write relev. bytes (r)<br />

PRE_MASK:=DBMASK_R; -- use right-hand side bit mask<br />

PRE_READ:=’1’ -- read dest. before writing<br />

when ((DBOS_R mod 8)/=7 -- if dest. isn’t byte-aligned<br />

or S(1 downto 0)/="00") -- or source and dest. are comb.<br />

else ’0’;<br />

else -- in between<br />

CAS_M:="0000"; -- write all 4 bytes<br />

PRE_READ:=’1’ -- only read destination<br />

when S(1 downto 0)/="00" -- if source and dest. are comb.<br />

else ’0’;<br />

PRE_MASK:=hi32; -- all GPU FIFO data bits valid<br />

end if;<br />

case GPU_FIFO_OUT is -- get data from GPU fifo buffer<br />

when 0 => D_GPU_FIFO:=D_GPU_FIFO0;<br />

when 1 => D_GPU_FIFO:=D_GPU_FIFO1;<br />

when 2 => D_GPU_FIFO:=D_GPU_FIFO2;<br />

when 3 => D_GPU_FIFO:=D_GPU_FIFO3;<br />

when 4 => D_GPU_FIFO:=D_GPU_FIFO4;<br />

when 5 => D_GPU_FIFO:=D_GPU_FIFO5;<br />

when 6 => D_GPU_FIFO:=D_GPU_FIFO6;<br />

when 7 => D_GPU_FIFO:=D_GPU_FIFO7;<br />

when 8 => D_GPU_FIFO:=D_GPU_FIFO8;<br />

end case;<br />

RAM_D_W:=WRITE_DATA; -- from diagram PIXBLT_PATH<br />

end if;<br />

CAS_MASK:=CAS_M bor CAS_DONE; -- don’t read the same bytes again<br />

Abbildung 98: Speedchart-Diagramm TIM/CONTROL/MEM ACCESS/MEM ADDRESS<br />

Anhang D.2<br />

Seite 128