DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abschnitt 4.2<br />

Seite 24<br />

der letzten Position der SR ausgegeben werden, müssen die SR mit den Daten der nächsten Speicherzeile<br />

geladen werden. Der Reload-Zyklus muß dabei vor dem Datenwechsel beginnen, und der<br />

Zeitpunkt des Wechsels wird den VRAMs im Laufe des Zyklus über eine Steuerleitung signalisiert.<br />

Nur auf diese Weise ist ein kontinuierlicher Bilddatenstrom zu erreichen. Ohne die Fähigkeit zu<br />

Midline Reloads wäre die Länge einer Videozeile auf die Schieberegisterlänge beschränkt.<br />

Abbildung 18: Beispiel für eine Verteilung<br />

von VRAM-Relaods: Ein Laden des<br />

Schieberegisters wird z. B. durch 0080<br />

gekennzeichnet, hier ist 00 die RAM-Zeile<br />

und 80 der SR-Zeiger (TAP).<br />

Es ist Panning aktiv (DPYSTRT = 0),<br />

und die virtuelle Zeilenlänge DPYINC ist<br />

größer als die physikalische.<br />

DPYSTRT = 0x0080 Worte<br />

DPYINC = 0x0220 Worte<br />

phys. Zeilenläge = 0x0140 Worte<br />

SRL = 256 Worte<br />

SRE = ’0’<br />

Zeile 0: 0080 0100<br />

ˆ<br />

0500<br />

ˆ<br />

0300<br />

ˆ<br />

0100<br />

Zeile 1: 02A0 0300<br />

Zeile 2: 04C0 0500<br />

4.2.2 ” Split Reloads“ und ” Non-Split Reloads“<br />

Zeile 3: 06E0 0700 0800<br />

ˆ ˆ<br />

0700 0800<br />

Zeile 4: 0900 0A00<br />

0A00<br />

Zeile 5: 0B20 0C00<br />

Um das kritische Timing der Midline Reloads zu entschärfen, bieten moderne Video-RAMs die<br />

Möglichkeit, nur eine Hälfte des Schieberegisters zu laden. Aus der anderen Hälfte können<br />

dabei gleichzeitig Daten seriell ausgegeben werden. Dies zeigt, daß die VRAMs keine echten Schieberegister,<br />

sondern zählergesteuerte Multiplexer enthalten. Über das Register-Bit SRE kann programmiert<br />

werden, ob die angeschlossenen VRAMs solche ” Split Reloads“ unterstützen (SRE=’1’:<br />

Split-Reload-Modus).<br />

Auch im Split-Reload-Modus erfolgt für jede Videozeile ein Newline Reload am Ende der vorigen<br />

Videozeile. Beginnen die Daten dabei in der unteren Hälfte des SR’s (wie in Zeile 4 und 5 in<br />

Abbildung 19), so enthalten bereits beide SR-Hälften Daten, die in der folgenden Zeile benötigt<br />

werden. Beginnt die Ausgabe hingegen in der oberen SR-Hälfte, so kann bereits unmittelbar nach<br />

dem Newline Reload die untere SR-Hälfte mit Daten aus der nächsten VRAM-Zeile geladen werden<br />

(Zeile 0–3, Abb. 19).<br />

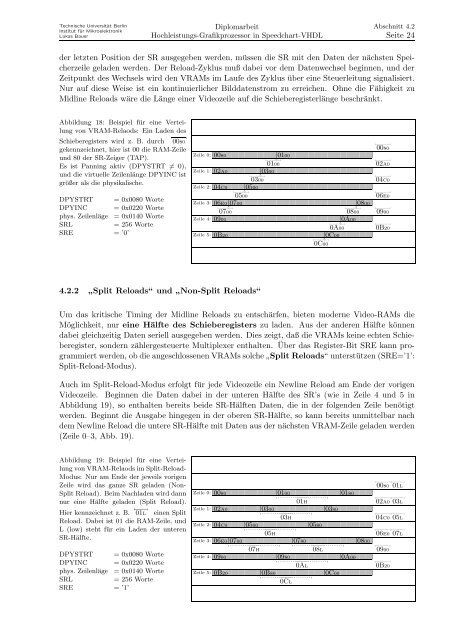

Abbildung 19: Beispiel für eine Verteilung<br />

von VRAM-Relaods im Split-Reload-<br />

Modus: Nur am Ende der jeweils vorigen<br />

Zeile wird das ganze SR geladen (Non-<br />

Split Reload). Beim Nachladen wird dann<br />

nur eine Hälfte geladen (Split Reload).<br />

Hier kennzeichnet z. B. 01L einen Split<br />

Reload. Dabei ist 01 die RAM-Zeile, und<br />

L (low) steht für ein Laden der unteren<br />

SR-Hälfte.<br />

DPYSTRT = 0x0080 Worte<br />

DPYINC = 0x0220 Worte<br />

phys. Zeilenläge = 0x0140 Worte<br />

SRL = 256 Worte<br />

SRE = ’1’<br />

ˆ<br />

0C00<br />

Zeile 0: 0080 0100 0180<br />

01H<br />

Zeile 1: 02A0 0300 0380<br />

03H<br />

Zeile 2: 04C0 0500 0580<br />

05H<br />

Zeile 3: 06E0 0700 0780 0800<br />

07H 08L<br />

Zeile 4: 0900 0980 0A00<br />

0CL<br />

0AL<br />

Zeile 5: 0B20 0B80 0C00<br />

ˆ<br />

0080<br />

02A0<br />

04C0<br />

06E0<br />

0900<br />

0B20<br />

0080 01L<br />

02A0 03L<br />

04C0 05L<br />

06E0 07L<br />

0900<br />

0B20