DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Current setting:<br />

Synchronous mode: Synthesis Silcsyn<br />

External clock: MClk_in<br />

Rising edge<br />

Period: 1 ns<br />

External reset: RESET_in<br />

Active level high<br />

Asynchronous reset<br />

Resolution scale: ps<br />

Time scale: ns<br />

Language: VHDL-like<br />

Design Variable:<br />

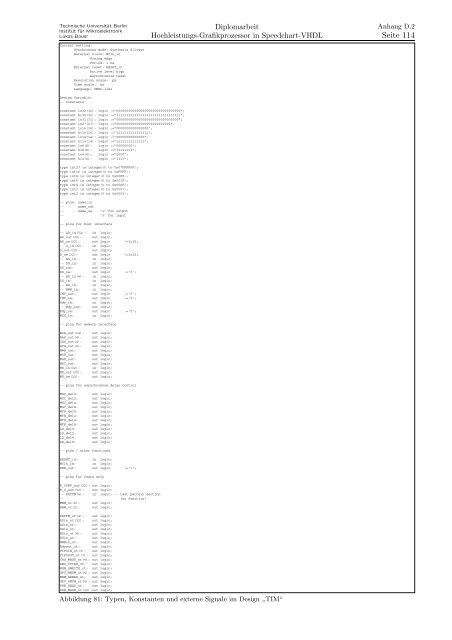

-- constants<br />

constant lo32(32): logic :="00000000000000000000000000000000";<br />

constant hi32(32): logic :="11111111111111111111111111111111";<br />

constant lo31(31): logic :="0000000000000000000000000000000";<br />

constant lo27(27): logic :="000000000000000000000000000";<br />

constant lo16(16): logic :="0000000000000000";<br />

constant hi16(16): logic :="1111111111111111";<br />

constant lo14(14): logic :="00000000000000";<br />

constant hi14(14): logic :="11111111111111";<br />

constant lo8(8): logic :="00000000";<br />

constant hi8(8): logic :="11111111";<br />

constant lo4(4): logic :="0000";<br />

constant hi4(4): logic :="1111";<br />

type int27 is integer(0 to 0x07FFFFFF);<br />

type int16 is integer(0 to 0xFFFF);<br />

type int8 is integer(0 to 0x00FF);<br />

type int5 is integer(0 to 0x001F);<br />

type int4 is integer(0 to 0x000F);<br />

type int3 is integer(0 to 0x0007);<br />

type int2 is integer(0 to 0x0003);<br />

-- pins: name_in<br />

-- name_out<br />

-- name_oe ’1’ for output<br />

-- ’0’ for input<br />

-- pins for host interface<br />

-- AD_in(32): in logic;<br />

AD_out(32): out logic;<br />

AD_oe(32): out logic :=lo32;<br />

-- D_in(32): in logic;<br />

D_out(32): out logic;<br />

D_oe(32): out logic :=lo32;<br />

-- AS_in: in logic;<br />

-- DS_in: in logic;<br />

DS_out: out logic;<br />

DS_oe: out logic :=’0’;<br />

-- BS_in(4): in logic;<br />

CS_in: in logic;<br />

-- RS_in: in logic;<br />

-- HWE_in: in logic;<br />

INT_out: out logic :=’0’;<br />

INT_oe: out logic :=’0’;<br />

Rdy_in: in logic;<br />

-- Rdy_out: out logic;<br />

Rdy_oe: out logic :=’0’;<br />

MUX_in: in logic;<br />

-- pins for memory interface<br />

RCA_out(14): out logic;<br />

RAS_out(4): out logic;<br />

CAS_out(4): out logic;<br />

ACS_out(4): out logic;<br />

MWE_out: out logic;<br />

MOE_out: out logic;<br />

MSF_out: out logic;<br />

MSC_out: out logic;<br />

MD_in(32): in logic;<br />

MD_out(32): out logic;<br />

MD_oe(32): out logic;<br />

-- pins for asynchronous delay control<br />

MSC_del0: out logic;<br />

MSC_del2: out logic;<br />

MSC_del4: out logic;<br />

MSC_del8: out logic;<br />

MTR_del0: out logic;<br />

MTR_del2: out logic;<br />

MTR_del4: out logic;<br />

MTR_del8: out logic;<br />

LD_del0: out logic;<br />

LD_del2: out logic;<br />

LD_del4: out logic;<br />

LD_del8: out logic;<br />

-- pins / other functions<br />

RESET_in: in logic;<br />

MClk_in: in logic;<br />

DWE_out: out logic :=’1’;<br />

-- pins for tests only<br />

R_CONF_out(32): out logic;<br />

R_4_out(32): out logic;<br />

-- PATTN(4): in logic; -- test pattern section<br />

-- (no function)<br />

MBW_ot(2): out logic;<br />

HBW_ot(2): out logic;<br />

PATTN_ot(4): out logic;<br />

ADin_ot(32): out logic;<br />

ASin_ot: out logic;<br />

DSin_ot: out logic;<br />

BSin_ot(4): out logic;<br />

RSin_ot: out logic;<br />

HWEin_ot: out logic;<br />

Rdyout_ot: out logic;<br />

FIFOIN_ot(3): out logic;<br />

FIFOOUT_ot(3): out logic;<br />

CAS_MASK_ot(4): out logic;<br />

ANY_CYCLE_ot: out logic;<br />

MEM_GWRITE_ot: out logic;<br />

GPU_WNUM_ot(4): out logic;<br />

MEM_GREAD_ot: out logic;<br />

GPU_RNUM_ot(4): out logic;<br />

PRE_READ_ot: out logic;<br />

PRE_MASK_ot(32):out logic;<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abbildung 81: Typen, Konstanten und externe Signale im Design ” TIM“<br />

Anhang D.2<br />

Seite 114