DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

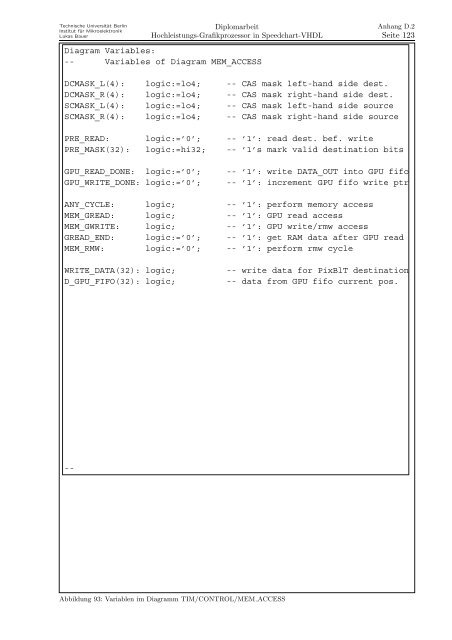

Diagram Variables:<br />

-- Variables of Diagram MEM_ACCESS<br />

Anhang D.2<br />

Seite 123<br />

DCMASK_L(4): logic:=lo4; -- CAS mask left-hand side dest.<br />

DCMASK_R(4): logic:=lo4; -- CAS mask right-hand side dest.<br />

SCMASK_L(4): logic:=lo4; -- CAS mask left-hand side source<br />

SCMASK_R(4): logic:=lo4; -- CAS mask right-hand side source<br />

PRE_READ: logic:=’0’; -- ’1’: read dest. bef. write<br />

PRE_MASK(32): logic:=hi32; -- ’1’s mark valid destination bits<br />

GPU_READ_DONE: logic:=’0’; -- ’1’: write DATA_OUT into GPU fifo<br />

GPU_WRITE_DONE: logic:=’0’; -- ’1’: increment GPU fifo write ptr<br />

ANY_CYCLE: logic; -- ’1’: perform memory access<br />

MEM_GREAD: logic; -- ’1’: GPU read access<br />

MEM_GWRITE: logic; -- ’1’: GPU write/rmw access<br />

GREAD_END: logic:=’0’; -- ’1’: get RAM data after GPU read<br />

MEM_RMW: logic:=’0’; -- ’1’: perform rmw cycle<br />

WRITE_DATA(32): logic; -- write data for PixBlT destination<br />

D_GPU_FIFO(32): logic; -- data from GPU fifo current pos.<br />

--<br />

Abbildung 93: Variablen im Diagramm TIM/CONTROL/MEM ACCESS