DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

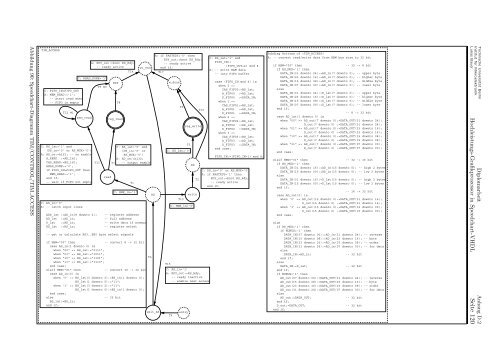

Abbildung 90: Speedchart-Diagramm TIM/CONTROL/TIM ACCESS<br />

TIM_ACCESS<br />

C: FIFO_IN=FIFO_OUT<br />

A: MEM_READ:=’1’;<br />

-- start read when<br />

-- FIFO is empty<br />

T12 #1<br />

C: RS_lat=’1’ and<br />

(DS_in=’0’ or RS_MUX=’0’)<br />

A: AD_oe:=hi32; -- oe enable<br />

A_READ :=AD_lat;<br />

CAS_READ:=BS_lat;<br />

READ_DONE:=’0’;<br />

if FIFO_IN=FIFO_OUT then<br />

MEM_READ:=’1’;<br />

end if;<br />

-- wait if FIFO not empty<br />

C: AS_in=’0’<br />

A: -- latch input lines<br />

A: RDY_out:=bnot RS_Rdy;<br />

-- ready active<br />

C: READ_DONE=’1’<br />

mem_read<br />

T11<br />

T9 #0<br />

read<br />

T7<br />

RDY<br />

T8<br />

reg_read<br />

T14<br />

ADS_lat :=AD_in(8 downto 2); -- register address<br />

AD_lat :=AD_in; -- full address<br />

D_lat :=AD_in; -- write data if nonmux<br />

RS_lat :=RS_in; -- register select<br />

-- get or calculate BS3..BS0 byte select signals<br />

C: RS_lat=’0’ and<br />

(DS_in=’0’ or<br />

RS_MUX=’0’)<br />

A: AD_oe:=hi32;<br />

-- output enable<br />

T1<br />

C: HWE_in=’1’<br />

wt_end<br />

if HBW="00" then -- convert 8 -> 32 bit<br />

case AD_in(1 downto 0) is<br />

when "00" => BS_lat:="0111";<br />

when "01" => BS_lat:="1011";<br />

when "10" => BS_lat:="1101";<br />

when "11" => BS_lat:="1110";<br />

end case;<br />

elsif HBW="01" then -- convert 16 -> 32 bit<br />

case AD_in(0) is<br />

when ’0’ => BS_lat(3 downto 2):=BS_in(1 downto 0);<br />

BS_lat(1 downto 0):="11";<br />

when ’1’ => BS_lat(3 downto 2):="11";<br />

BS_lat(1 downto 0):=BS_in(1 downto 0);<br />

end case;<br />

else -- 32 bit<br />

BS_lat:=BS_in;<br />

end if;<br />

T5<br />

AS<br />

wait_AS<br />

A: if FASTRDY=’0’ then<br />

RDY_out:=bnot RS_Rdy;<br />

-- ready active<br />

end if;<br />

T17<br />

T15<br />

w_done<br />

T4<br />

T6<br />

T13<br />

entry<br />

reg_write<br />

T3<br />

C: RS_lat=’0’<br />

DS<br />

write<br />

C: HWE_in=’0’<br />

T2<br />

T10<br />

C: AS_in=’1’<br />

A: RDY_out:=RS_Rdy;<br />

-- ready inactive<br />

-- enable next access<br />

C: RS_lat=’1’ and<br />

FIFO_IN/=<br />

(FIFO_OUT+4) mod 8<br />

A: -- write RAM data<br />

-- into FIFO buffer<br />

case (FIFO_IN mod 4) is<br />

when 0 =><br />

CAS_FIFO0:=BS_lat;<br />

A_FIFO0 :=AD_lat;<br />

D_FIFO0 :=DATA_IN;<br />

when 1 =><br />

CAS_FIFO1:=BS_lat;<br />

A_FIFO1 :=AD_lat;<br />

D_FIFO1 :=DATA_IN;<br />

when 2 =><br />

CAS_FIFO2:=BS_lat;<br />

A_FIFO2 :=AD_lat;<br />

D_FIFO2 :=DATA_IN;<br />

when 3 =><br />

CAS_FIFO3:=BS_lat;<br />

A_FIFO3 :=AD_lat;<br />

D_FIFO3 :=DATA_IN;<br />

end case;<br />

FIFO_IN:=(FIFO_IN+1) mod 8;<br />

C: DS_in=’0’ or RS_MUX=’0’<br />

A: if FASTRDY=’1’ then<br />

RDY_out:=bnot RS_Rdy;<br />

-- ready active<br />

end if;<br />

Subdiag Actions of <br />

A: -- convert read/write data from HBW bus size to 32 bit<br />

if HBW="00" then -- 32 -> 8 bit<br />

if RS_MUX=’1’ then<br />

DATA_IN(31 downto 24):=AD_in(7 downto 0); -- upper byte<br />

DATA_IN(23 downto 16):=AD_in(7 downto 0); -- higher byte<br />

DATA_IN(15 downto 08):=AD_in(7 downto 0); -- middle byte<br />

DATA_IN(07 downto 00):=AD_in(7 downto 0); -- lower byte<br />

else<br />

DATA_IN(31 downto 24):=D_lat(7 downto 0); -- upper byte<br />

DATA_IN(23 downto 16):=D_lat(7 downto 0); -- higher byte<br />

DATA_IN(15 downto 08):=D_lat(7 downto 0); -- middle byte<br />

DATA_IN(07 downto 00):=D_lat(7 downto 0); -- lower byte<br />

end if;<br />

-- 8 -> 32 bit<br />

case AD_lat(1 downto 0) is<br />

when "00" => AD_out(7 downto 0):=DATA_OUT(31 downto 24);<br />

D_out(7 downto 0) :=DATA_OUT(31 downto 24);<br />

when "01" => AD_out(7 downto 0):=DATA_OUT(23 downto 16);<br />

D_out(7 downto 0) :=DATA_OUT(23 downto 16);<br />

when "10" => AD_out(7 downto 0):=DATA_OUT(15 downto 08);<br />

D_out(7 downto 0) :=DATA_OUT(15 downto 08);<br />

when "11" => AD_out(7 downto 0):=DATA_OUT(07 downto 00);<br />

D_out(7 downto 0) :=DATA_OUT(07 downto 00);<br />

end case;<br />

elsif HBW="01" then -- 32 -> 16 bit<br />

if RS_MUX=’1’ then<br />

DATA_IN(31 downto 16):=AD_in(15 downto 0); -- high 2 bytes<br />

DATA_IN(15 downto 00):=AD_in(15 downto 0); -- low 2 bytes<br />

else<br />

DATA_IN(31 downto 16):=D_lat(15 downto 0); -- high 2 bytes<br />

DATA_IN(15 downto 00):=D_lat(15 downto 0); -- low 2 bytes<br />

end if;<br />

-- 16 -> 32 bit<br />

case AD_lat(0) is<br />

when ’0’ => AD_out(15 downto 0):=DATA_OUT(31 downto 16);<br />

D_out(15 downto 0) :=DATA_OUT(31 downto 16);<br />

when ’1’ => AD_out(15 downto 0):=DATA_OUT(15 downto 00);<br />

D_out(15 downto 0) :=DATA_OUT(15 downto 00);<br />

end case;<br />

else<br />

if RS_MUX=’1’ then<br />

if NUBUS=’1’ then<br />

DATA_IN(07 downto 00):=AD_in(31 downto 24); -- reverse<br />

DATA_IN(15 downto 08):=AD_in(23 downto 16); -- byte<br />

DATA_IN(23 downto 16):=AD_in(15 downto 08); -- order<br />

DATA_IN(31 downto 24):=AD_in(07 downto 00); -- for data<br />

else<br />

DATA_IN:=AD_in; -- 32 bit<br />

end if;<br />

else<br />

DATA_IN:=D_lat; -- 32 bit<br />

end if;<br />

if NUBUS=’1’ then<br />

AD_out(07 downto 00):=DATA_OUT(31 downto 24); -- reverse<br />

AD_out(15 downto 08):=DATA_OUT(23 downto 16); -- byte<br />

AD_out(23 downto 16):=DATA_OUT(15 downto 08); -- order<br />

AD_out(31 downto 24):=DATA_OUT(07 downto 00); -- for data<br />

else<br />

AD_out:=DATA_OUT; -- 32 bit<br />

end if;<br />

D_out:=DATA_OUT; -- 32 bit<br />

end if;<br />

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Anhang D.2<br />

Seite 120