DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

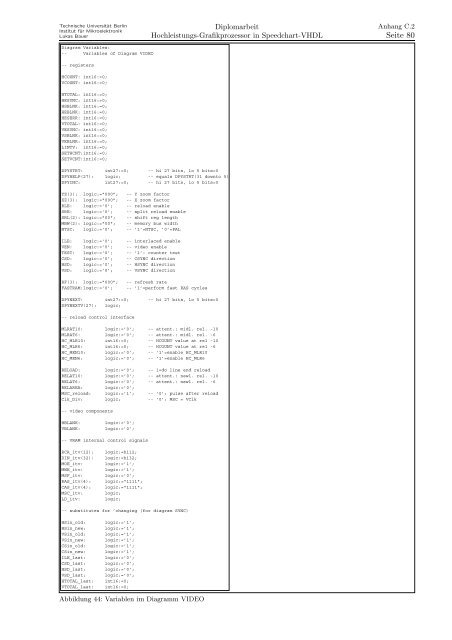

Diagram Variables:<br />

-- Variables of Diagram VIDEO<br />

-- registers<br />

HCOUNT: int16:=0;<br />

VCOUNT: int16:=0;<br />

HTOTAL: int16:=0;<br />

HESYNC: int16:=0;<br />

HSBLNK: int16:=0;<br />

HEBLNK: int16:=0;<br />

HESERR: int16:=0;<br />

VTOTAL: int16:=0;<br />

VESYNC: int16:=0;<br />

VSBLNK: int16:=0;<br />

VEBLNK: int16:=0;<br />

LINTV: int16:=0;<br />

SETHCNT:int16:=0;<br />

SETVCNT:int16:=0;<br />

DPYSTRT: int27:=0; -- hi 27 bits, lo 5 bits=0<br />

DPYHELP(27): logic; -- equals DPYSTRT(31 downto 5)<br />

DPYINC: int27:=0; -- hi 27 bits, lo 5 bits=0<br />

YZ(3): logic:="000"; -- Y zoom factor<br />

XZ(3): logic:="000"; -- X zoom factor<br />

RLE: logic:=’0’; -- reload enable<br />

SRE: logic:=’0’; -- split reload enable<br />

SRL(2): logic:="00"; -- shift reg length<br />

MBW(2): logic:="00"; -- memory bus width<br />

NTSC: logic:=’0’; -- ’1’=NTSC, ’0’=PAL<br />

ILE: logic:=’0’; -- interlaced enable<br />

VEN: logic:=’0’; -- video enable<br />

TEST: logic:=’0’; -- ’1’: counter test<br />

CSD: logic:=’0’; -- CSYNC direction<br />

HSD: logic:=’0’; -- HSYNC direction<br />

VSD: logic:=’0’; -- VSYNC direction<br />

RF(3): logic:="000"; -- refresh rate<br />

FASTRAM:logic:=’0’; -- ’1’=perform fast RAS cycles<br />

DPYNEXT: int27:=0; -- hi 27 bits, lo 5 bits=0<br />

DPYNEXTV(27): logic;<br />

-- reload control interface<br />

MLRAT10: logic:=’0’; -- attent.: midl. rel. -10<br />

MLRAT6: logic:=’0’; -- attent.: midl. rel. -6<br />

HC_MLR10: int16:=0; -- HCOUNT value at rel -10<br />

HC_MLR6: int16:=0; -- HCOUNT value at rel -6<br />

HC_MEN10: logic:=’0’; -- ’1’=enable HC_MLR10<br />

HC_MEN6: logic:=’0’; -- ’1’=enable HC_MLR6<br />

RELOAD: logic:=’0’; -- 1=do line end reload<br />

RELAT10: logic:=’0’; -- attent.: newl. rel. -10<br />

RELAT6: logic:=’0’; -- attent.: newl. rel. -6<br />

RELAREA: logic:=’0’;<br />

MSC_reload: logic:=’1’; -- ’0’: pulse after reload<br />

Clk_Div: logic; -- ’0’: MSC = VClk<br />

-- video components<br />

HBLANK: logic:=’0’;<br />

VBLANK: logic:=’0’;<br />

-- VRAM internal control signals<br />

RCA_itv(12): logic:=hi12;<br />

DIN_itv(32): logic:=hi32;<br />

MOE_itv: logic:=’1’;<br />

MWE_itv: logic:=’1’;<br />

MSF_itv: logic:=’0’;<br />

RAS_itv(4): logic:="1111";<br />

CAS_itv(4): logic:="1111";<br />

MSC_itv: logic;<br />

LD_itv: logic;<br />

-- substitutes for ’changing (for diagram SYNC)<br />

HSin_old: logic:=’1’;<br />

HSin_new: logic:=’1’;<br />

VSin_old: logic:=’1’;<br />

VSin_new: logic:=’1’;<br />

CSin_old: logic:=’1’;<br />

CSin_new: logic:=’1’;<br />

ILE_last: logic:=’0’;<br />

CSD_last: logic:=’0’;<br />

HSD_last: logic:=’0’;<br />

VSD_last: logic:=’0’;<br />

HTOTAL_last: int16:=0;<br />

VTOTAL_last: int16:=0;<br />

Abbildung 44: Variablen im Diagramm VIDEO<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Anhang C.2<br />

Seite 80