DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

3.2 Interne Synchronisation<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

3.2.1 Vollbildbetrieb (Non-Interlaced Mode)<br />

Abschnitt 3.2<br />

Seite 12<br />

Bei interner Synchronisation im Vollbildbetrieb bestimmen TIM-interne Register auf einfache Weise<br />

den zeitlichen Verlauf der Synchronisations-Signale.<br />

Ein Horizontal-Zähler HCOUNT zählt dabei die steigenden Flanken des Videotaktes VClk und<br />

wird nach Erreichen des Registerwertes HTOTAL auf Null zurückgesetzt.<br />

Die horizontalen Sync- und Blanking-Signale werden von HCOUNT abgeleitet. So wird HSYNC<br />

beim Zählerüberlauf aktiv ’0’ und nach Erreichen von HESYNC wieder inaktiv ’1’. HBLANK,<br />

die Komponente des CBLANK-Signals, die das Bild während der horizontalen Strahlrücklaufphase<br />

dunkeltastet, wird nach HCOUNT=HSBLNK aktiv ’0’ und nach HCOUNT=HEBLNK inaktiv ’1’.<br />

Ein Vertikal-Zähler VCOUNT wird mit jedem Überlauf von HCOUNT erhöht und nach Erreichen<br />

des Registerwertes VTOTAL auf Null zurückgesetzt. Aus VCOUNT leiten sich die vertikalen<br />

Signale VSYNC und VBLANK in entsprechender Weise ab, nur die Bedingung für das Ende des<br />

VSYNC-Pulses ist VCOUNT=VESYNC/2 und nicht VCOUNT=VESYNC.<br />

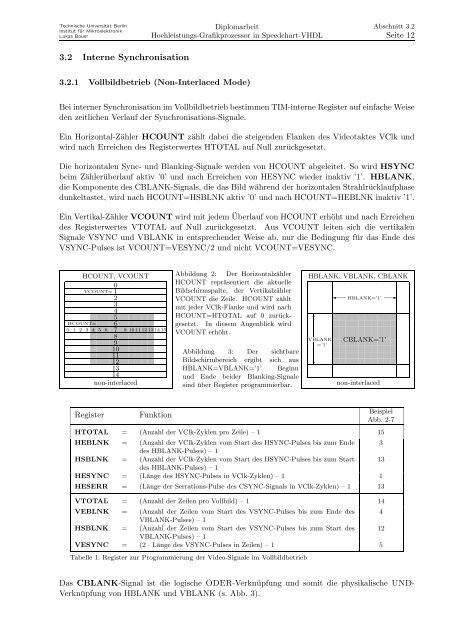

HCOUNT, VCOUNT Abbildung 2: Der Horizontalzähler HBLANK, VBLANK, CBLANK<br />

0<br />

HCOUNT repräsentiert die aktuelle<br />

VCOUNT= 1<br />

Bildschirmspalte, der Vertikalzähler<br />

2<br />

VCOUNT die Zeile. HCOUNT zählt<br />

✛ HBLANK=’1’ ✲<br />

3<br />

mit jeder VClk-Flanke und wird nach<br />

4<br />

5<br />

HCOUNT=HTOTAL auf 0 zurück-<br />

✻<br />

6<br />

gesetzt. In diesem Augenblick wird<br />

7<br />

VCOUNT erhöht.<br />

8<br />

VBLANK<br />

9<br />

CBLANK=’1’<br />

=’1’<br />

10<br />

Abbildung 3: Der sichtbare<br />

11<br />

12<br />

Bildschirmbereich ergibt sich aus ❄<br />

13<br />

HBLANK=VBLANK=’1’. Beginn<br />

14<br />

und Ende beider Blanking-Signale<br />

non-interlaced<br />

sind über Register programmierbar.<br />

non-interlaced<br />

HCOUNT=<br />

0 1 2 3 4 5 6 9 10 11 12 13 14 15<br />

Register Funktion<br />

Beispiel<br />

Abb. 2-7<br />

HTOTAL = (Anzahl der VClk-Zyklen pro Zeile) – 1 15<br />

HEBLNK = (Anzahl der VClk-Zyklen vom Start des HSYNC-Pulses bis zum Ende<br />

des HBLANK-Pulses) – 1<br />

3<br />

HSBLNK = (Anzahl der VClk-Zyklen vom Start des HSYNC-Pulses bis zum Start<br />

des HBLANK-Pulses) – 1<br />

13<br />

HESYNC = (Länge des HSYNC-Pulses in VClk-Zyklen) – 1 1<br />

HESERR = (Länge der Serrations-Pulse des CSYNC-Signals in VClk-Zyklen) – 1 13<br />

VTOTAL = (Anzahl der Zeilen pro Vollbild) – 1 14<br />

VEBLNK = (Anzahl der Zeilen vom Start des VSYNC-Pulses bis zum Ende des<br />

VBLANK-Pulses) – 1<br />

4<br />

HSBLNK = (Anzahl der Zeilen vom Start des VSYNC-Pulses bis zum Start des<br />

VBLANK-Pulses) – 1<br />

12<br />

VESYNC = (2 · Länge des VSYNC-Pulses in Zeilen) – 1 5<br />

Tabelle 1: Register zur Programmierung der Video-Signale im Vollbildbetrieb<br />

Das CBLANK-Signal ist die logische ODER-Verknüpfung und somit die physikalische UND-<br />

Verknüpfung von HBLANK und VBLANK (s. Abb. 3).