DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abschnitt 2.2<br />

Seite 8<br />

RAMs liegen, soll eine gemischte Bestückung mit VRAMs und DRAMs möglich sein. Zur Darstellung<br />

müssen die Daten aus den DRAMs in die VRAMs kopiert werden.<br />

Der im Rahmen dieser Arbeit zu entwickelnde Grafikprozessor ” TIM“ soll gemäß der Spezifikation<br />

[1] allen Anforderungen an einen modernen Hochleistungs-Grafikprozessor gerecht werden.<br />

Er soll zum TI-34020 in wesentlichen Punkten kompatibel sein, der Befehlssatz soll jedoch auf<br />

Befehle beschränkt sein, die auf rechteckigen Bildschirmbereichen arbeiten, da diese bei Desktop-<br />

Anwendungen fast ausschließlich verwendet werden. So soll z. B. das Ziehen diagonaler Linien<br />

nicht unterstützt werden. Stattdessen soll eine deutlich höhere Bearbeitungsgeschwindigkeit als<br />

beim TI-34020 erreicht werden.<br />

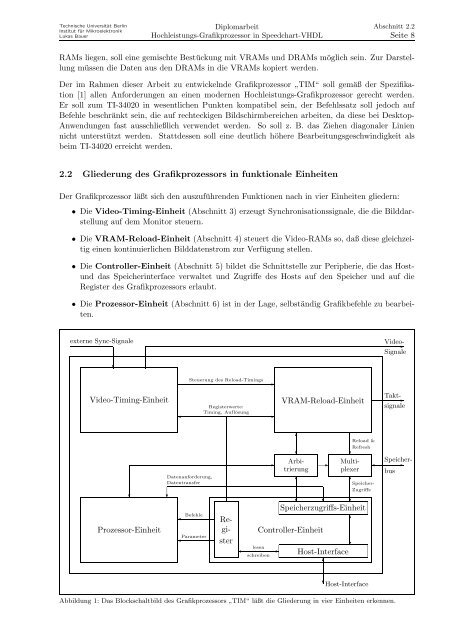

2.2 Gliederung des Grafikprozessors in funktionale Einheiten<br />

Der Grafikprozessor läßt sich den auszuführenden Funktionen nach in vier Einheiten gliedern:<br />

• Die Video-Timing-Einheit (Abschnitt 3) erzeugt Synchronisationssignale, die die Bilddarstellung<br />

auf dem Monitor steuern.<br />

• Die VRAM-Reload-Einheit (Abschnitt 4) steuert die Video-RAMs so, daß diese gleichzeitig<br />

einen kontinuierlichen Bilddatenstrom zur Verfügung stellen.<br />

• Die Controller-Einheit (Abschnitt 5) bildet die Schnittstelle zur Peripherie, die das Hostund<br />

das Speicherinterface verwaltet und Zugriffe des Hosts auf den Speicher und auf die<br />

Register des Grafikprozessors erlaubt.<br />

• Die Prozessor-Einheit (Abschnitt 6) ist in der Lage, selbständig Grafikbefehle zu bearbeiten.<br />

externe Sync-Signale<br />

❄<br />

Video-Timing-Einheit VRAM-Reload-Einheit<br />

✛<br />

Datenanforderung,<br />

Datentransfer<br />

Steuerung des Reload-Timings<br />

Registerwerte:<br />

Timing, Auflösung<br />

❄ ❄<br />

✲ Multiplexer<br />

✛ ✲<br />

✻<br />

✻<br />

Speicherbus<br />

Arbitrierung<br />

Speicher-<br />

Zugriffe<br />

❄ ❄<br />

❄ ❄ ❄<br />

Befehle ✛ Re-<br />

Speicherzugriffs-Einheit<br />

Prozessor-Einheit gi Controller-Einheit<br />

Parameter ✛ ster<br />

✛ ✲ Host-Interface<br />

lesen<br />

✻<br />

❄<br />

schreiben<br />

✲<br />

✲<br />

✲<br />

✻<br />

✻<br />

Reload &<br />

Refresh<br />

❄ Host-Interface<br />

Abbildung 1: Das Blockschaltbild des Grafikprozessors ” TIM“ läßt die Gliederung in vier Einheiten erkennen.<br />

Video- ✲<br />

Signale<br />

Takt✲<br />

signale