DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

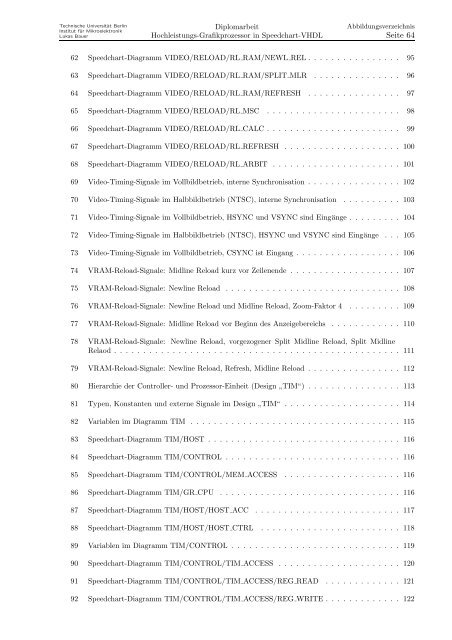

Abbildungsverzeichnis<br />

Seite 64<br />

62 Speedchart-Diagramm VIDEO/RELOAD/RL RAM/NEWL REL . . . . . . . . . . . . . . . . 95<br />

63 Speedchart-Diagramm VIDEO/RELOAD/RL RAM/SPLIT MLR . . . . . . . . . . . . . . . 96<br />

64 Speedchart-Diagramm VIDEO/RELOAD/RL RAM/REFRESH . . . . . . . . . . . . . . . . 97<br />

65 Speedchart-Diagramm VIDEO/RELOAD/RL MSC . . . . . . . . . . . . . . . . . . . . . . . 98<br />

66 Speedchart-Diagramm VIDEO/RELOAD/RL CALC . . . . . . . . . . . . . . . . . . . . . . . 99<br />

67 Speedchart-Diagramm VIDEO/RELOAD/RL REFRESH . . . . . . . . . . . . . . . . . . . . 100<br />

68 Speedchart-Diagramm VIDEO/RELOAD/RL ARBIT . . . . . . . . . . . . . . . . . . . . . . 101<br />

69 Video-Timing-Signale im Vollbildbetrieb, interne Synchronisation . . . . . . . . . . . . . . . . 102<br />

70 Video-Timing-Signale im Halbbildbetrieb (NTSC), interne Synchronisation . . . . . . . . . . 103<br />

71 Video-Timing-Signale im Vollbildbetrieb, HSYNC und VSYNC sind Eingänge . . . . . . . . . 104<br />

72 Video-Timing-Signale im Halbbildbetrieb (NTSC), HSYNC und VSYNC sind Eingänge . . . 105<br />

73 Video-Timing-Signale im Vollbildbetrieb, CSYNC ist Eingang . . . . . . . . . . . . . . . . . . 106<br />

74 VRAM-Reload-Signale: Midline Reload kurz vor Zeilenende . . . . . . . . . . . . . . . . . . . 107<br />

75 VRAM-Reload-Signale: Newline Reload . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108<br />

76 VRAM-Reload-Signale: Newline Reload und Midline Reload, Zoom-Faktor 4 . . . . . . . . . 109<br />

77 VRAM-Reload-Signale: Midline Reload vor Beginn des Anzeigebereichs . . . . . . . . . . . . 110<br />

78 VRAM-Reload-Signale: Newline Reload, vorgezogener Split Midline Reload, Split Midline<br />

Relaod . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111<br />

79 VRAM-Reload-Signale: Newline Reload, Refresh, Midline Reload . . . . . . . . . . . . . . . . 112<br />

80 Hierarchie der Controller- und Prozessor-Einheit (Design ” TIM“) . . . . . . . . . . . . . . . . 113<br />

81 Typen, Konstanten und externe Signale im Design ” TIM“ . . . . . . . . . . . . . . . . . . . . 114<br />

82 Variablen im Diagramm TIM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115<br />

83 Speedchart-Diagramm TIM/HOST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116<br />

84 Speedchart-Diagramm TIM/CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116<br />

85 Speedchart-Diagramm TIM/CONTROL/MEM ACCESS . . . . . . . . . . . . . . . . . . . . 116<br />

86 Speedchart-Diagramm TIM/GR CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116<br />

87 Speedchart-Diagramm TIM/HOST/HOST ACC . . . . . . . . . . . . . . . . . . . . . . . . . 117<br />

88 Speedchart-Diagramm TIM/HOST/HOST CTRL . . . . . . . . . . . . . . . . . . . . . . . . 118<br />

89 Variablen im Diagramm TIM/CONTROL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119<br />

90 Speedchart-Diagramm TIM/CONTROL/TIM ACCESS . . . . . . . . . . . . . . . . . . . . . 120<br />

91 Speedchart-Diagramm TIM/CONTROL/TIM ACCESS/REG READ . . . . . . . . . . . . . 121<br />

92 Speedchart-Diagramm TIM/CONTROL/TIM ACCESS/REG WRITE . . . . . . . . . . . . . 122