DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

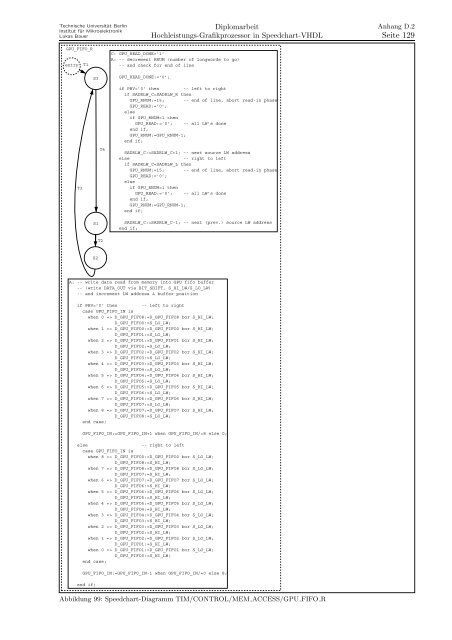

GPU_FIFO_R<br />

entry<br />

T3<br />

T1<br />

S1<br />

S2<br />

T4<br />

T2<br />

A: -- write data read from memory into GPU fifo buffer<br />

-- (write DATA_OUT via BIT_SHIFT, S_HI_LW/S_LO_LW)<br />

-- and increment LW address & buffer position<br />

if PBV=’0’ then -- left to right<br />

case GPU_FIFO_IN is<br />

when 0 => D_GPU_FIFO8:=D_GPU_FIFO8 bor S_HI_LW;<br />

D_GPU_FIFO0:=S_LO_LW;<br />

when 1 => D_GPU_FIFO0:=D_GPU_FIFO0 bor S_HI_LW;<br />

D_GPU_FIFO1:=S_LO_LW;<br />

when 2 => D_GPU_FIFO1:=D_GPU_FIFO1 bor S_HI_LW;<br />

D_GPU_FIFO2:=S_LO_LW;<br />

when 3 => D_GPU_FIFO2:=D_GPU_FIFO2 bor S_HI_LW;<br />

D_GPU_FIFO3:=S_LO_LW;<br />

when 4 => D_GPU_FIFO3:=D_GPU_FIFO3 bor S_HI_LW;<br />

D_GPU_FIFO4:=S_LO_LW;<br />

when 5 => D_GPU_FIFO4:=D_GPU_FIFO4 bor S_HI_LW;<br />

D_GPU_FIFO5:=S_LO_LW;<br />

when 6 => D_GPU_FIFO5:=D_GPU_FIFO5 bor S_HI_LW;<br />

D_GPU_FIFO6:=S_LO_LW;<br />

when 7 => D_GPU_FIFO6:=D_GPU_FIFO6 bor S_HI_LW;<br />

D_GPU_FIFO7:=S_LO_LW;<br />

when 8 => D_GPU_FIFO7:=D_GPU_FIFO7 bor S_HI_LW;<br />

D_GPU_FIFO8:=S_LO_LW;<br />

end case;<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

GPU_FIFO_IN:=GPU_FIFO_IN+1 when GPU_FIFO_IN/=8 else 0;<br />

else -- right to left<br />

case GPU_FIFO_IN is<br />

when 8 => D_GPU_FIFO0:=D_GPU_FIFO0 bor S_LO_LW;<br />

D_GPU_FIFO8:=S_HI_LW;<br />

when 7 => D_GPU_FIFO8:=D_GPU_FIFO8 bor S_LO_LW;<br />

D_GPU_FIFO7:=S_HI_LW;<br />

when 6 => D_GPU_FIFO7:=D_GPU_FIFO7 bor S_LO_LW;<br />

D_GPU_FIFO6:=S_HI_LW;<br />

when 5 => D_GPU_FIFO6:=D_GPU_FIFO6 bor S_LO_LW;<br />

D_GPU_FIFO5:=S_HI_LW;<br />

when 4 => D_GPU_FIFO5:=D_GPU_FIFO5 bor S_LO_LW;<br />

D_GPU_FIFO4:=S_HI_LW;<br />

when 3 => D_GPU_FIFO4:=D_GPU_FIFO4 bor S_LO_LW;<br />

D_GPU_FIFO3:=S_HI_LW;<br />

when 2 => D_GPU_FIFO3:=D_GPU_FIFO3 bor S_LO_LW;<br />

D_GPU_FIFO2:=S_HI_LW;<br />

when 1 => D_GPU_FIFO2:=D_GPU_FIFO2 bor S_LO_LW;<br />

D_GPU_FIFO1:=S_HI_LW;<br />

when 0 => D_GPU_FIFO1:=D_GPU_FIFO1 bor S_LO_LW;<br />

D_GPU_FIFO0:=S_HI_LW;<br />

end case;<br />

GPU_FIFO_IN:=GPU_FIFO_IN-1 when GPU_FIFO_IN/=0 else 8;<br />

end if;<br />

S3<br />

C: GPU_READ_DONE=’1’<br />

A: -- decrement RNUM (number of longwords to go)<br />

-- and check for end of line<br />

GPU_READ_DONE:=’0’;<br />

if PBV=’0’ then -- left to right<br />

if SADRLW_C=SADRLW_R then<br />

GPU_RNUM:=15; -- end of line, abort read-in phase<br />

GPU_READ:=’0’;<br />

else<br />

if GPU_RNUM=1 then<br />

GPU_READ:=’0’; -- all LW’s done<br />

end if;<br />

GPU_RNUM:=GPU_RNUM-1;<br />

end if;<br />

SADRLW_C:=SADRLW_C+1; -- next source LW address<br />

else -- right to left<br />

if SADRLW_C=SADRLW_L then<br />

GPU_RNUM:=15; -- end of line, abort read-in phase<br />

GPU_READ:=’0’;<br />

else<br />

if GPU_RNUM=1 then<br />

GPU_READ:=’0’; -- all LW’s done<br />

end if;<br />

GPU_RNUM:=GPU_RNUM-1;<br />

end if;<br />

SADRLW_C:=SADRLW_C-1; -- next (prev.) source LW address<br />

end if;<br />

Abbildung 99: Speedchart-Diagramm TIM/CONTROL/MEM ACCESS/GPU FIFO R<br />

Anhang D.2<br />

Seite 129