DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

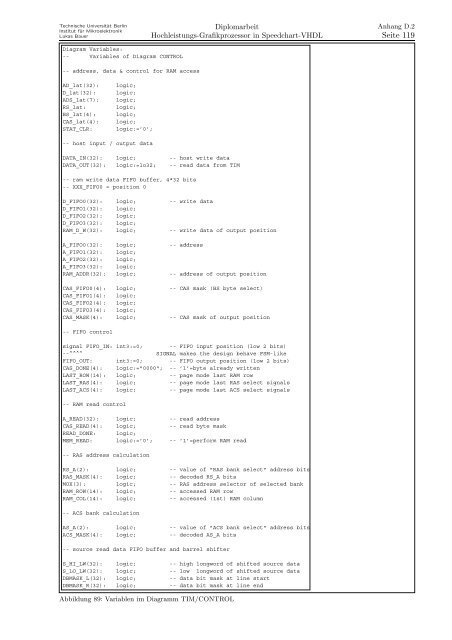

Diagram Variables:<br />

-- Variables of Diagram CONTROL<br />

-- address, data & control for RAM access<br />

AD_lat(32): logic;<br />

D_lat(32): logic;<br />

ADS_lat(7): logic;<br />

RS_lat: logic;<br />

BS_lat(4): logic;<br />

CAS_lat(4): logic;<br />

STAT_CLR: logic:=’0’;<br />

-- host input / output data<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

DATA_IN(32): logic; -- host write data<br />

DATA_OUT(32): logic:=lo32; -- read data from TIM<br />

-- ram write data FIFO buffer, 4*32 bits<br />

-- XXX_FIFO0 = position 0<br />

D_FIFO0(32): logic; -- write data<br />

D_FIFO1(32): logic;<br />

D_FIFO2(32): logic;<br />

D_FIFO3(32): logic;<br />

RAM_D_W(32): logic; -- write data of output position<br />

A_FIFO0(32): logic; -- address<br />

A_FIFO1(32): logic;<br />

A_FIFO2(32): logic;<br />

A_FIFO3(32): logic;<br />

RAM_ADDR(32): logic; -- address of output position<br />

CAS_FIFO0(4): logic; -- CAS mask (BS byte select)<br />

CAS_FIFO1(4): logic;<br />

CAS_FIFO2(4): logic;<br />

CAS_FIFO3(4): logic;<br />

CAS_MASK(4): logic; -- CAS mask of output position<br />

-- FIFO control<br />

signal FIFO_IN: int3:=0; -- FIFO input position (low 2 bits)<br />

--^^^^ SIGNAL makes the design behave FSM-like<br />

FIFO_OUT: int3:=0; -- FIFO output position (low 2 bits)<br />

CAS_DONE(4): logic:="0000"; -- ’1’=byte already written<br />

LAST_ROW(14): logic; -- page mode last RAM row<br />

LAST_RAS(4): logic; -- page mode last RAS select signals<br />

LAST_ACS(4): logic; -- page mode last ACS select signals<br />

-- RAM read control<br />

A_READ(32): logic; -- read address<br />

CAS_READ(4): logic; -- read byte mask<br />

READ_DONE: logic;<br />

MEM_READ: logic:=’0’; -- ’1’=perform RAM read<br />

-- RAS address calculation<br />

RS_A(2): logic; -- value of "RAS bank select" address bits<br />

RAS_MASK(4): logic; -- decoded RS_A bits<br />

MOX(3): logic; -- RAS address selector of selected bank<br />

RAM_ROW(14): logic; -- accessed RAM row<br />

RAM_COL(14): logic; -- accessed (1st) RAM column<br />

-- ACS bank calculation<br />

AS_A(2): logic; -- value of "ACS bank select" address bits<br />

ACS_MASK(4): logic; -- decoded AS_A bits<br />

-- source read data FIFO buffer and barrel shifter<br />

S_HI_LW(32): logic; -- high longword of shifted source data<br />

S_LO_LW(32): logic; -- low longword of shifted source data<br />

DBMASK_L(32): logic; -- data bit mask at line start<br />

DBMASK_R(32): logic; -- data bit mask at line end<br />

Abbildung 89: Variablen im Diagramm TIM/CONTROL<br />

Anhang D.2<br />

Seite 119