DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

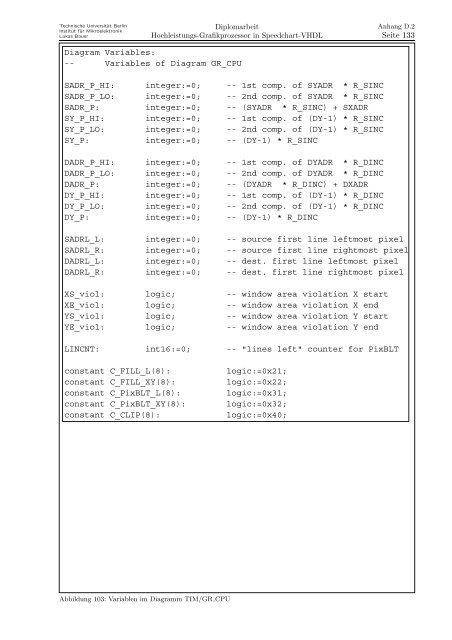

Diagram Variables:<br />

-- Variables of Diagram GR_CPU<br />

SADR_P_HI: integer:=0; -- 1st comp. of SYADR * R_SINC<br />

SADR_P_LO: integer:=0; -- 2nd comp. of SYADR * R_SINC<br />

SADR_P: integer:=0; -- (SYADR * R_SINC) + SXADR<br />

SY_P_HI: integer:=0; -- 1st comp. of (DY-1) * R_SINC<br />

SY_P_LO: integer:=0; -- 2nd comp. of (DY-1) * R_SINC<br />

SY_P: integer:=0; -- (DY-1) * R_SINC<br />

DADR_P_HI: integer:=0; -- 1st comp. of DYADR * R_DINC<br />

DADR_P_LO: integer:=0; -- 2nd comp. of DYADR * R_DINC<br />

DADR_P: integer:=0; -- (DYADR * R_DINC) + DXADR<br />

DY_P_HI: integer:=0; -- 1st comp. of (DY-1) * R_DINC<br />

DY_P_LO: integer:=0; -- 2nd comp. of (DY-1) * R_DINC<br />

DY_P: integer:=0; -- (DY-1) * R_DINC<br />

Anhang D.2<br />

Seite 133<br />

SADRL_L: integer:=0; -- source first line leftmost pixel<br />

SADRL_R: integer:=0; -- source first line rightmost pixel<br />

DADRL_L: integer:=0; -- dest. first line leftmost pixel<br />

DADRL_R: integer:=0; -- dest. first line rightmost pixel<br />

XS_viol: logic; -- window area violation X start<br />

XE_viol: logic; -- window area violation X end<br />

YS_viol: logic; -- window area violation Y start<br />

YE_viol: logic; -- window area violation Y end<br />

LINCNT: int16:=0; -- "lines left" counter for PixBLT<br />

constant C_FILL_L(8): logic:=0x21;<br />

constant C_FILL_XY(8): logic:=0x22;<br />

constant C_PixBLT_L(8): logic:=0x31;<br />

constant C_PixBLT_XY(8): logic:=0x32;<br />

constant C_CLIP(8): logic:=0x40;<br />

Abbildung 103: Variablen im Diagramm TIM/GR CPU