DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

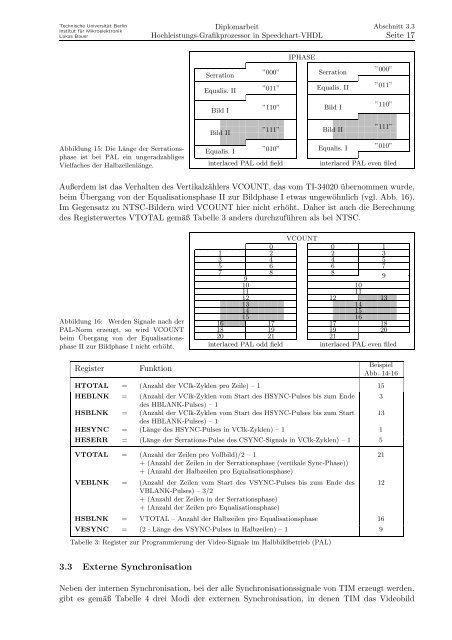

Abbildung 15: Die Länge der Serrationsphase<br />

ist bei PAL ein ungeradzahliges<br />

Vielfaches der Halbzeilenlänge.<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Serration<br />

Equalis. II<br />

Bild I<br />

Bild II<br />

Equalis. I<br />

”000”<br />

”011”<br />

”110”<br />

”111”<br />

”010”<br />

interlaced PAL odd field<br />

IPHASE<br />

Serration<br />

Equalis. II<br />

Bild I<br />

Bild II<br />

Equalis. I<br />

Abschnitt 3.3<br />

Seite 17<br />

”000”<br />

”011”<br />

”110”<br />

”111”<br />

”010”<br />

interlaced PAL even filed<br />

Außerdem ist das Verhalten des Vertikalzählers VCOUNT, das vom TI-34020 übernommen wurde,<br />

beim Übergang von der Equalisationsphase II zur Bildphase I etwas ungewöhnlich (vgl. Abb. 16).<br />

Im Gegensatz zu NTSC-Bildern wird VCOUNT hier nicht erhöht. Daher ist auch die Berechnung<br />

des Registerwertes VTOTAL gemäß Tabelle 3 anders durchzuführen als bei NTSC.<br />

Abbildung 16: Werden Signale nach der<br />

PAL-Norm erzeugt, so wird VCOUNT<br />

beim Übergang von der Equalisationsphase<br />

II zur Bildphase I nicht erhöht.<br />

Register Funktion<br />

VCOUNT<br />

1<br />

3<br />

5<br />

7<br />

16<br />

18<br />

20<br />

9<br />

10<br />

11<br />

12<br />

13<br />

14<br />

15<br />

0<br />

2<br />

4<br />

6<br />

8<br />

17<br />

19<br />

21<br />

0<br />

2<br />

4<br />

6<br />

8<br />

12<br />

17<br />

19<br />

21<br />

10<br />

11<br />

14<br />

15<br />

16<br />

1<br />

3<br />

5<br />

7<br />

9<br />

13<br />

18<br />

20<br />

interlaced PAL odd field<br />

interlaced PAL even filed<br />

Beispiel<br />

Abb. 14-16<br />

HTOTAL = (Anzahl der VClk-Zyklen pro Zeile) – 1 15<br />

HEBLNK = (Anzahl der VClk-Zyklen vom Start des HSYNC-Pulses bis zum Ende<br />

des HBLANK-Pulses) – 1<br />

3<br />

HSBLNK = (Anzahl der VClk-Zyklen vom Start des HSYNC-Pulses bis zum Start<br />

des HBLANK-Pulses) – 1<br />

13<br />

HESYNC = (Länge des HSYNC-Pulses in VClk-Zyklen) – 1 1<br />

HESERR = (Länge der Serrations-Pulse des CSYNC-Signals in VClk-Zyklen) – 1 5<br />

VTOTAL = (Anzahl der Zeilen pro Vollbild)/2 – 1<br />

+ (Anzahl der Zeilen in der Serrationsphase (vertikale Sync-Phase))<br />

+ (Anzahl der Halbzeilen pro Equalisationsphase)<br />

VEBLNK = (Anzahl der Zeilen vom Start des VSYNC-Pulses bis zum Ende des<br />

VBLANK-Pulses) – 3/2<br />

+ (Anzahl der Zeilen in der Serrationsphase)<br />

+ (Anzahl der Zeilen pro Equalisationsphase)<br />

HSBLNK = VTOTAL – Anzahl der Halbzeilen pro Equalisationsphase 16<br />

VESYNC = (2 · Länge des VSYNC-Pulses in Halbzeilen) – 1 9<br />

Tabelle 3: Register zur Programmierung der Video-Signale im Halbbildbetrieb (PAL)<br />

3.3 Externe Synchronisation<br />

Neben der internen Synchronisation, bei der alle Synchronisationssignale von TIM erzeugt werden,<br />

gibt es gemäß Tabelle 4 drei Modi der externen Synchronisation, in denen TIM das Videobild<br />

21<br />

12