DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abschnitt 5.2<br />

Seite 36<br />

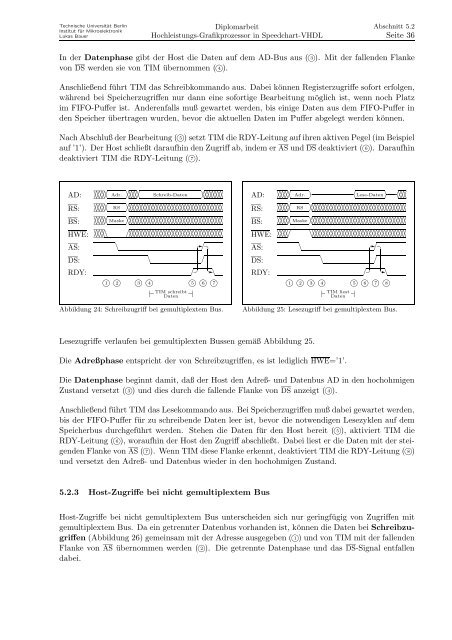

In der Datenphase gibt der Host die Daten auf dem AD-Bus aus ( ❤ 3 ). Mit der fallenden Flanke<br />

von DS werden sie von TIM übernommen ( ❤ 4 ).<br />

Anschließend führt TIM das Schreibkommando aus. Dabei können Registerzugriffe sofort erfolgen,<br />

während bei Speicherzugriffen nur dann eine sofortige Bearbeitung möglich ist, wenn noch Platz<br />

im FIFO-Puffer ist. Anderenfalls muß gewartet werden, bis einige Daten aus dem FIFO-Puffer in<br />

den Speicher übertragen wurden, bevor die aktuellen Daten im Puffer abgelegt werden können.<br />

Nach Abschluß der Bearbeitung ( ❤ 5 ) setzt TIM die RDY-Leitung auf ihren aktiven Pegel (im Beispiel<br />

auf ’1’). Der Host schließt daraufhin den Zugriff ab, indem er AS und DS deaktiviert ( ❤ 6 ). Daraufhin<br />

deaktiviert TIM die RDY-Leitung ( ❤ 7 ).<br />

AD: \/\/\/\/\/ Adr. \/\/\/\/\/ Schreib-Daten \/\/\/\/\/\/\/\/<br />

RS: \/\/\/\/\/ RS \/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/<br />

BS:<br />

\/\/\/\/\/ Maske \/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/<br />

HWE: \/\/\/\/\ /\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/<br />

AS: \ ✄✲ / <br />

DS: \ /<br />

RDY: / ✁ ✂✲ \<br />

❤1 ❤ 2 ❤ 3 ❤ 4 ❤ 5 ❤ 6 ❤ 7<br />

TIM schreibt<br />

Daten<br />

AD: \/\/\/\/\/ Adr. 〉 〈Lese-Daten〉 〈\/\/\/<br />

RS: \/\/\/\/\/ RS \/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/<br />

BS:<br />

\/\/\/\/\/ Maske \/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/<br />

HWE: \/\/\/\// \\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/<br />

AS: \ ✄✲ / <br />

DS: \ /<br />

RDY: / ✁ ✂✲ \<br />

❤1 ❤ 2 ❤ 3 ❤ 4 ❤ 5 ❤ 6 ❤ 7 ❤ 8<br />

TIM liest<br />

Daten<br />

Abbildung 24: Schreibzugriff bei gemultiplextem Bus. Abbildung 25: Lesezugriff bei gemultiplextem Bus.<br />

Lesezugriffe verlaufen bei gemultiplexten Bussen gemäß Abbildung 25.<br />

Die Adreßphase entspricht der von Schreibzugriffen, es ist lediglich HWE=’1’.<br />

Die Datenphase beginnt damit, daß der Host den Adreß- und Datenbus AD in den hochohmigen<br />

Zustand versetzt ( ❤ 3 ) und dies durch die fallende Flanke von DS anzeigt ( ❤ 4 ).<br />

Anschließend führt TIM das Lesekommando aus. Bei Speicherzugriffen muß dabei gewartet werden,<br />

bis der FIFO-Puffer für zu schreibende Daten leer ist, bevor die notwendigen Lesezyklen auf dem<br />

Speicherbus durchgeführt werden. Stehen die Daten für den Host bereit ( ❤ 5 ), aktiviert TIM die<br />

RDY-Leitung ( ❤ 6 ), woraufhin der Host den Zugriff abschließt. Dabei liest er die Daten mit der steigenden<br />

Flanke von AS ( ❤ 7 ). Wenn TIM diese Flanke erkennt, deaktiviert TIM die RDY-Leitung ( ❤ 8 )<br />

und versetzt den Adreß- und Datenbus wieder in den hochohmigen Zustand.<br />

5.2.3 Host-Zugriffe bei nicht gemultiplextem Bus<br />

Host-Zugriffe bei nicht gemultiplextem Bus unterscheiden sich nur geringfügig von Zugriffen mit<br />

gemultiplextem Bus. Da ein getrennter Datenbus vorhanden ist, können die Daten bei Schreibzugriffen<br />

(Abbildung 26) gemeinsam mit der Adresse ausgegeben ( ❤ 1 ) und von TIM mit der fallenden<br />

Flanke von AS übernommen werden ( ❤ 2 ). Die getrennte Datenphase und das DS-Signal entfallen<br />

dabei.