DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

3.4 Realisierung in Speedchart-VHDL<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abschnitt 3.4<br />

Seite 19<br />

Im Speedchart-Design besteht die Video-Timing-Einheit aus drei Diagrammen. Das Diagramm<br />

S HCNT steuert das Horizontaltiming, das Diagramm S VCNT das Vertikaltiming. Das Diagramm<br />

CSYNC ist nur im externen Synchronisationsmodus wichtig, um aus einem externen<br />

CSYNC-Signal die VSYNC-Information zu extrahieren.<br />

3.4.1 Steuerung des horizontalen Timings<br />

Das Diagramm S HCNT (Seite 82) steuert das Horizontaltiming, also den Zähler HCOUNT, die<br />

Signale HSYNC, CSYNC und HBLANK, das DPYNEXT-Register, sowie die Reload-Anforderung.<br />

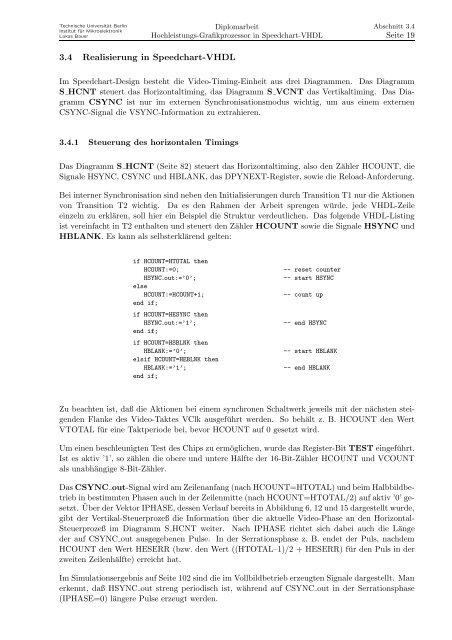

Bei interner Synchronisation sind neben den Initialisierungen durch Transition T1 nur die Aktionen<br />

von Transition T2 wichtig. Da es den Rahmen der Arbeit sprengen würde, jede VHDL-Zeile<br />

einzeln zu erklären, soll hier ein Beispiel die Struktur verdeutlichen. Das folgende VHDL-Listing<br />

ist vereinfacht in T2 enthalten und steuert den Zähler HCOUNT sowie die Signale HSYNC und<br />

HBLANK. Es kann als selbsterklärend gelten:<br />

if HCOUNT=HTOTAL then<br />

HCOUNT:=0; -- reset counter<br />

HSYNC out:=’0’; -- start HSYNC<br />

else<br />

HCOUNT:=HCOUNT+1; -- count up<br />

end if;<br />

if HCOUNT=HESYNC then<br />

HSYNC out:=’1’; -- end HSYNC<br />

end if;<br />

if HCOUNT=HSBLNK then<br />

HBLANK:=’0’; -- start HBLANK<br />

elsif HCOUNT=HEBLNK then<br />

HBLANK:=’1’; -- end HBLANK<br />

end if;<br />

Zu beachten ist, daß die Aktionen bei einem synchronen Schaltwerk jeweils mit der nächsten steigenden<br />

Flanke des Video-Taktes VClk ausgeführt werden. So behält z. B. HCOUNT den Wert<br />

VTOTAL für eine Taktperiode bei, bevor HCOUNT auf 0 gesetzt wird.<br />

Um einen beschleunigten Test des Chips zu ermöglichen, wurde das Register-Bit TEST eingeführt.<br />

Ist es aktiv ’1’, so zählen die obere und untere Hälfte der 16-Bit-Zähler HCOUNT und VCOUNT<br />

als unabhängige 8-Bit-Zähler.<br />

Das CSYNC out-Signal wird am Zeilenanfang (nach HCOUNT=HTOTAL) und beim Halbbildbetrieb<br />

in bestimmten Phasen auch in der Zeilenmitte (nach HCOUNT=HTOTAL/2) auf aktiv ’0’ gesetzt.<br />

Über der Vektor IPHASE, dessen Verlauf bereits in Abbildung 6, 12 und 15 dargestellt wurde,<br />

gibt der Vertikal-Steuerprozeß die Information über die aktuelle Video-Phase an den Horizontal-<br />

Steuerprozeß im Diagramm S HCNT weiter. Nach IPHASE richtet sich dabei auch die Länge<br />

der auf CSYNC out ausgegebenen Pulse. In der Serrationsphase z. B. endet der Puls, nachdem<br />

HCOUNT den Wert HESERR (bzw. den Wert ((HTOTAL–1)/2 + HESERR) für den Puls in der<br />

zweiten Zeilenhälfte) erreicht hat.<br />

Im Simulationsergebnis auf Seite 102 sind die im Vollbildbetrieb erzeugten Signale dargestellt. Man<br />

erkennt, daß HSYNC out streng periodisch ist, während auf CSYNC out in der Serrationsphase<br />

(IPHASE=0) längere Pulse erzeugt werden.