DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

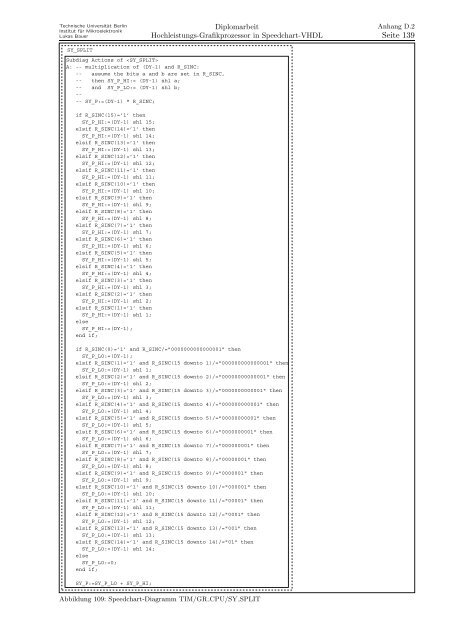

SY_SPLIT<br />

Subdiag Actions of <br />

A: -- multiplication of (DY-1) and R_SINC:<br />

-- assume the bits a and b are set in R_SINC,<br />

-- then SY_P_HI:= (DY-1) shl a;<br />

-- and SY_P_LO:= (DY-1) shl b;<br />

--<br />

-- SY_P:=(DY-1) * R_SINC;<br />

if R_SINC(15)=’1’ then<br />

SY_P_HI:=(DY-1) shl 15;<br />

elsif R_SINC(14)=’1’ then<br />

SY_P_HI:=(DY-1) shl 14;<br />

elsif R_SINC(13)=’1’ then<br />

SY_P_HI:=(DY-1) shl 13;<br />

elsif R_SINC(12)=’1’ then<br />

SY_P_HI:=(DY-1) shl 12;<br />

elsif R_SINC(11)=’1’ then<br />

SY_P_HI:=(DY-1) shl 11;<br />

elsif R_SINC(10)=’1’ then<br />

SY_P_HI:=(DY-1) shl 10;<br />

elsif R_SINC(9)=’1’ then<br />

SY_P_HI:=(DY-1) shl 9;<br />

elsif R_SINC(8)=’1’ then<br />

SY_P_HI:=(DY-1) shl 8;<br />

elsif R_SINC(7)=’1’ then<br />

SY_P_HI:=(DY-1) shl 7;<br />

elsif R_SINC(6)=’1’ then<br />

SY_P_HI:=(DY-1) shl 6;<br />

elsif R_SINC(5)=’1’ then<br />

SY_P_HI:=(DY-1) shl 5;<br />

elsif R_SINC(4)=’1’ then<br />

SY_P_HI:=(DY-1) shl 4;<br />

elsif R_SINC(3)=’1’ then<br />

SY_P_HI:=(DY-1) shl 3;<br />

elsif R_SINC(2)=’1’ then<br />

SY_P_HI:=(DY-1) shl 2;<br />

elsif R_SINC(1)=’1’ then<br />

SY_P_HI:=(DY-1) shl 1;<br />

else<br />

SY_P_HI:=(DY-1);<br />

end if;<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

if R_SINC(0)=’1’ and R_SINC/="0000000000000001" then<br />

SY_P_LO:=(DY-1);<br />

elsif R_SINC(1)=’1’ and R_SINC(15 downto 1)/="000000000000001" then<br />

SY_P_LO:=(DY-1) shl 1;<br />

elsif R_SINC(2)=’1’ and R_SINC(15 downto 2)/="00000000000001" then<br />

SY_P_LO:=(DY-1) shl 2;<br />

elsif R_SINC(3)=’1’ and R_SINC(15 downto 3)/="0000000000001" then<br />

SY_P_LO:=(DY-1) shl 3;<br />

elsif R_SINC(4)=’1’ and R_SINC(15 downto 4)/="000000000001" then<br />

SY_P_LO:=(DY-1) shl 4;<br />

elsif R_SINC(5)=’1’ and R_SINC(15 downto 5)/="00000000001" then<br />

SY_P_LO:=(DY-1) shl 5;<br />

elsif R_SINC(6)=’1’ and R_SINC(15 downto 6)/="0000000001" then<br />

SY_P_LO:=(DY-1) shl 6;<br />

elsif R_SINC(7)=’1’ and R_SINC(15 downto 7)/="000000001" then<br />

SY_P_LO:=(DY-1) shl 7;<br />

elsif R_SINC(8)=’1’ and R_SINC(15 downto 8)/="00000001" then<br />

SY_P_LO:=(DY-1) shl 8;<br />

elsif R_SINC(9)=’1’ and R_SINC(15 downto 9)/="0000001" then<br />

SY_P_LO:=(DY-1) shl 9;<br />

elsif R_SINC(10)=’1’ and R_SINC(15 downto 10)/="000001" then<br />

SY_P_LO:=(DY-1) shl 10;<br />

elsif R_SINC(11)=’1’ and R_SINC(15 downto 11)/="00001" then<br />

SY_P_LO:=(DY-1) shl 11;<br />

elsif R_SINC(12)=’1’ and R_SINC(15 downto 12)/="0001" then<br />

SY_P_LO:=(DY-1) shl 12;<br />

elsif R_SINC(13)=’1’ and R_SINC(15 downto 13)/="001" then<br />

SY_P_LO:=(DY-1) shl 13;<br />

elsif R_SINC(14)=’1’ and R_SINC(15 downto 14)/="01" then<br />

SY_P_LO:=(DY-1) shl 14;<br />

else<br />

SY_P_LO:=0;<br />

end if;<br />

SY_P:=SY_P_LO + SY_P_HI;<br />

Abbildung 109: Speedchart-Diagramm TIM/GR CPU/SY SPLIT<br />

Anhang D.2<br />

Seite 139