DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abschnitt 3.2<br />

Seite 13<br />

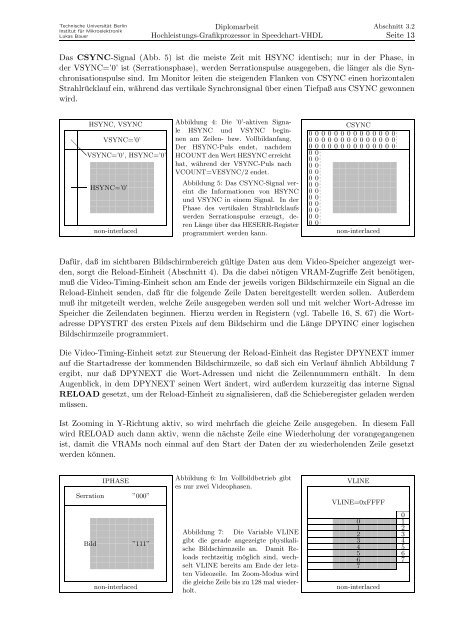

Das CSYNC-Signal (Abb. 5) ist die meiste Zeit mit HSYNC identisch; nur in der Phase, in<br />

der VSYNC=’0’ ist (Serrationsphase), werden Serrationspulse ausgegeben, die länger als die Synchronisationspulse<br />

sind. Im Monitor leiten die steigenden Flanken von CSYNC einen horizontalen<br />

Strahlrücklauf ein, während das vertikale Synchronsignal über einen Tiefpaß aus CSYNC gewonnen<br />

wird.<br />

HSYNC, VSYNC<br />

VSYNC=’0’<br />

❅<br />

❅VSYNC=’0’, HSYNC=’0’<br />

Abbildung 4: Die ’0’-aktiven Signale<br />

HSYNC und VSYNC beginnen<br />

am Zeilen- bzw. Vollbildanfang.<br />

Der HSYNC-Puls endet, nachdem<br />

HCOUNT den Wert HESYNC erreicht<br />

hat, während der VSYNC-Puls nach<br />

VCOUNT=VESYNC/2 endet.<br />

CSYNC<br />

0 0 0 0 0 0 0 0 0 0 0 0 0 0<br />

0 0 0 0 0 0 0 0 0 0 0 0 0 0<br />

0 0 0 0 0 0 0 0 0 0 0 0 0 0<br />

0 0<br />

HSYNC=’0’<br />

non-interlaced<br />

Abbildung 5: Das CSYNC-Signal vereint<br />

die Informationen von HSYNC<br />

und VSYNC in einem Signal. In der<br />

Phase des vertikalen Strahlrücklaufs<br />

werden Serrationspulse erzeugt, deren<br />

Länge über das HESERR-Register<br />

programmiert werden kann.<br />

0 0<br />

0 0<br />

0 0<br />

0 0<br />

0 0<br />

0 0<br />

0 0<br />

0 0<br />

0 0<br />

0 0<br />

0 0<br />

non-interlaced<br />

Dafür, daß im sichtbaren Bildschirmbereich gültige Daten aus dem Video-Speicher angezeigt werden,<br />

sorgt die Reload-Einheit (Abschnitt 4). Da die dabei nötigen VRAM-Zugriffe Zeit benötigen,<br />

muß die Video-Timing-Einheit schon am Ende der jeweils vorigen Bildschirmzeile ein Signal an die<br />

Reload-Einheit senden, daß für die folgende Zeile Daten bereitgestellt werden sollen. Außerdem<br />

muß ihr mitgeteilt werden, welche Zeile ausgegeben werden soll und mit welcher Wort-Adresse im<br />

Speicher die Zeilendaten beginnen. Hierzu werden in Registern (vgl. Tabelle 16, S. 67) die Wortadresse<br />

DPYSTRT des ersten Pixels auf dem Bildschirm und die Länge DPYINC einer logischen<br />

Bildschirmzeile programmiert.<br />

Die Video-Timing-Einheit setzt zur Steuerung der Reload-Einheit das Register DPYNEXT immer<br />

auf die Startadresse der kommenden Bildschirmzeile, so daß sich ein Verlauf ähnlich Abbildung 7<br />

ergibt, nur daß DPYNEXT die Wort-Adressen und nicht die Zeilennummern enthält. In dem<br />

Augenblick, in dem DPYNEXT seinen Wert ändert, wird außerdem kurzzeitig das interne Signal<br />

RELOAD gesetzt, um der Reload-Einheit zu signalisieren, daß die Schieberegister geladen werden<br />

müssen.<br />

Ist Zooming in Y-Richtung aktiv, so wird mehrfach die gleiche Zeile ausgegeben. In diesem Fall<br />

wird RELOAD auch dann aktiv, wenn die nächste Zeile eine Wiederholung der vorangegangenen<br />

ist, damit die VRAMs noch einmal auf den Start der Daten der zu wiederholenden Zeile gesetzt<br />

werden können.<br />

IPHASE<br />

Abbildung 6: Im Vollbildbetrieb gibt<br />

es nur zwei Videophasen.<br />

VLINE<br />

Serration ”000”<br />

VLINE=0xFFFF<br />

Bild ”111”<br />

non-interlaced<br />

Abbildung 7: Die Variable VLINE<br />

gibt die gerade angezeigte physikalische<br />

Bildschirmzeile an. Damit Reloads<br />

rechtzeitig möglich sind, wechselt<br />

VLINE bereits am Ende der letzten<br />

Videozeile. Im Zoom-Modus wird<br />

die gleiche Zeile bis zu 128 mal wiederholt.<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

non-interlaced<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7