DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

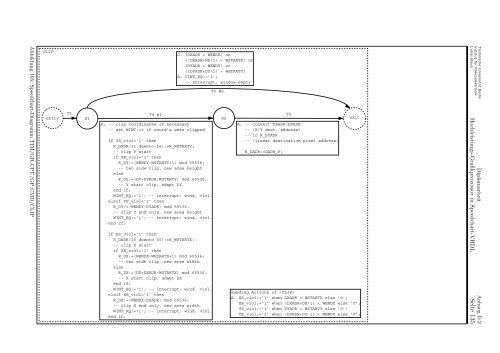

Abbildung 105: Speedchart-Diagramm TIM/GR CPU/GP CMD/CLIP<br />

CLIP<br />

entry<br />

T1<br />

S1<br />

T4 #1<br />

A: -- clip coordinates if necessary<br />

-- set WINT:=1 if coord’s were clipped<br />

if YS_viol=’1’ then<br />

R_DADR(31 downto 16):=R_WSTARTY;<br />

-- clip Y start<br />

if YE_viol=’1’ then<br />

R_DY:=(WENDY-WSTARTY+1) mod 65536;<br />

-- two side clip, new area height<br />

else<br />

R_DY:=(DY+DYADR-WSTARTY) mod 65536;<br />

-- Y start clip, adapt DY<br />

end if;<br />

WINT_RQ:=’1’; -- interrupt: wind. viol.<br />

elsif YE_viol=’1’ then<br />

R_DY:=(WENDY-DYADR) mod 65536;<br />

-- clip Y end only, new area height<br />

WINT_RQ:=’1’; -- interrupt: wind. viol.<br />

end if;<br />

if XS_viol=’1’ then<br />

R_DADR(15 downto 00):=R_WSTARTX;<br />

-- clip X start<br />

if XE_viol=’1’ then<br />

R_DX:=(WENDX-WSTARTX+1) mod 65536;<br />

-- two side clip, new area width<br />

else<br />

R_DX:=(DX+DXADR-WSTARTX) mod 65536;<br />

-- X start clip, adapt DX<br />

end if;<br />

WINT_RQ:=’1’; -- interrupt: wind. viol.<br />

elsif XE_viol=’1’ then<br />

R_DX:=(WENDX-DXADR) mod 65536;<br />

-- clip X end only, new area width<br />

WINT_RQ:=’1’; -- interrupt: wind. viol.<br />

end if;<br />

C: (DXADR > WENDX) or<br />

((DXADR+DX-1) < WSTARTX) or<br />

(DYADR > WENDY) or<br />

((DYADR+DY-1) < WSTARTY)<br />

A: CINT_RQ:=’1’;<br />

-- interrupt: window empty<br />

T5 #0<br />

S2<br />

T2<br />

A: -- convert DXADR/DYADR<br />

-- (X/Y dest. address)<br />

-- to R_DYADR<br />

-- (linear destination pixel address)<br />

R_DADR:=DADR_P;<br />

exit<br />

Subdiag Actions of <br />

A: XS_viol:=’1’ when DXADR < WSTARTX else ’0’;<br />

XE_viol:=’1’ when (DXADR+DX-1) < WENDX else ’0’;<br />

YS_viol:=’1’ when DYADR < WSTARTY else ’0’;<br />

YE_viol:=’1’ when (DYADR+DY-1) < WENDY else ’0’;<br />

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Anhang D.2<br />

Seite 135