DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abschnitt 3.3<br />

Seite 18<br />

synchron zu einem externen Videosignal aufbaut und so das Überlagern und Einblenden von Bildern<br />

ermöglicht.<br />

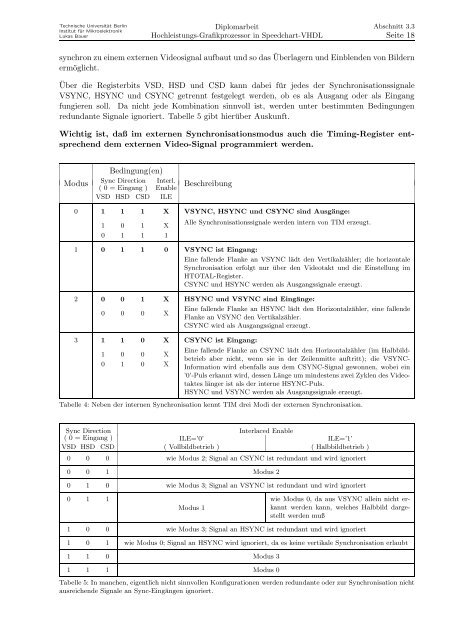

Über die Registerbits VSD, HSD und CSD kann dabei für jedes der Synchronisationssignale<br />

VSYNC, HSYNC und CSYNC getrennt festgelegt werden, ob es als Ausgang oder als Eingang<br />

fungieren soll. Da nicht jede Kombination sinnvoll ist, werden unter bestimmten Bedingungen<br />

redundante Signale ignoriert. Tabelle 5 gibt hierüber Auskunft.<br />

Wichtig ist, daß im externen Synchronisationsmodus auch die Timing-Register entsprechend<br />

dem externen Video-Signal programmiert werden.<br />

Modus<br />

0 1<br />

Bedingung(en)<br />

Sync Direction<br />

( 0 = Eingang )<br />

Interl.<br />

Enable Beschreibung<br />

VSD HSD CSD ILE<br />

1<br />

0<br />

1<br />

0<br />

1<br />

1<br />

1<br />

1<br />

X<br />

X<br />

1<br />

VSYNC, HSYNC und CSYNC sind Ausgänge:<br />

Alle Synchronisationssignale werden intern von TIM erzeugt.<br />

1 0 1 1 0 VSYNC ist Eingang:<br />

Eine fallende Flanke an VSYNC lädt den Vertikalzähler; die horizontale<br />

Synchronisation erfolgt nur über den Videotakt und die Einstellung im<br />

HTOTAL-Register.<br />

CSYNC und HSYNC werden als Ausgangssignale erzeugt.<br />

2 0<br />

0<br />

3 1<br />

1<br />

0<br />

0<br />

0<br />

1<br />

0<br />

1<br />

1<br />

0<br />

0<br />

0<br />

0<br />

X<br />

X<br />

X<br />

X<br />

X<br />

HSYNC und VSYNC sind Eingänge:<br />

Eine fallende Flanke an HSYNC lädt den Horizontalzähler, eine fallende<br />

Flanke an VSYNC den Vertikalzähler.<br />

CSYNC wird als Ausgangssignal erzeugt.<br />

CSYNC ist Eingang:<br />

Eine fallende Flanke an CSYNC lädt den Horizontalzähler (im Halbbildbetrieb<br />

aber nicht, wenn sie in der Zeilenmitte auftritt); die VSYNC-<br />

Information wird ebenfalls aus dem CSYNC-Signal gewonnen, wobei ein<br />

’0’-Puls erkannt wird, dessen Länge um mindestens zwei Zyklen des Videotaktes<br />

länger ist als der interne HSYNC-Puls.<br />

HSYNC und VSYNC werden als Ausgangssignale erzeugt.<br />

Tabelle 4: Neben der internen Synchronisation kennt TIM drei Modi der externen Synchronisation.<br />

Sync Direction Interlaced Enable<br />

( 0 = Eingang ) ILE=’0’ ILE=’1’<br />

VSD HSD CSD ( Vollbildbetrieb ) ( Halbbildbetrieb )<br />

0 0 0 wie Modus 2; Signal an CSYNC ist redundant und wird ignoriert<br />

0 0 1 Modus 2<br />

0 1 0 wie Modus 3; Signal an VSYNC ist redundant und wird ignoriert<br />

0 1 1<br />

Modus 1<br />

wie Modus 0, da aus VSYNC allein nicht erkannt<br />

werden kann, welches Halbbild dargestellt<br />

werden muß<br />

1 0 0 wie Modus 3; Signal an HSYNC ist redundant und wird ignoriert<br />

1 0 1 wie Modus 0; Signal an HSYNC wird ignoriert, da es keine vertikale Synchronisation erlaubt<br />

1 1 0 Modus 3<br />

1 1 1 Modus 0<br />

Tabelle 5: In manchen, eigentlich nicht sinnvollen Konfigurationen werden redundante oder zur Synchronisation nicht<br />

ausreichende Signale an Sync-Eingängen ignoriert.