DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

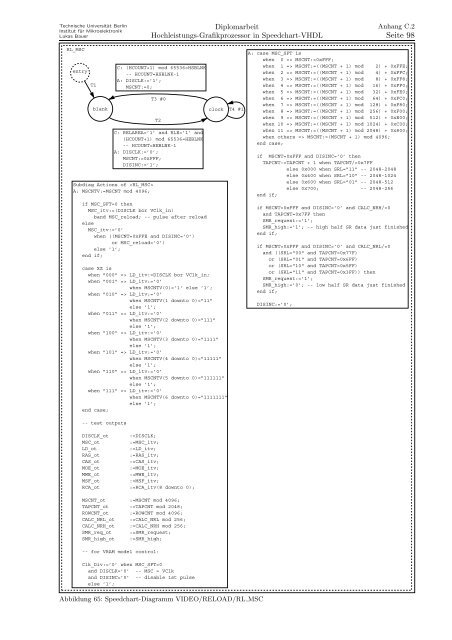

RL_MSC<br />

entry<br />

T1<br />

blank<br />

Subdiag Actions of <br />

A: MSCNTV:=MSCNT mod 4096;<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

C: (HCOUNT+1) mod 65536=HSBLNK<br />

-- HCOUNT=HSBLNK-1<br />

A: DISCLK:=’1’;<br />

MSCNT:=0;<br />

T3 #0<br />

T2<br />

C: RELAREA=’1’ and RLE=’1’ and<br />

(HCOUNT+1) mod 65536=HEBLNK<br />

-- HCOUNT=HEBLNK-1<br />

A: DISCLK:=’0’;<br />

MSCNT:=0xFFF;<br />

DISINC:=’1’;<br />

if MSC_SFT=0 then<br />

MSC_itv:=(DISCLK bor VClk_in)<br />

band MSC_reload; -- pulse after reload<br />

else<br />

MSC_itv:=’0’<br />

when ((MSCNT=0xFFE and DISINC=’0’)<br />

or MSC_reload=’0’)<br />

else ’1’;<br />

end if;<br />

clock<br />

case XZ is<br />

when "000" => LD_itv:=DISCLK bor VClk_in;<br />

when "001" => LD_itv:=’0’<br />

when MSCNTV(0)=’1’ else ’1’;<br />

when "010" => LD_itv:=’0’<br />

when MSCNTV(1 downto 0)="11"<br />

else ’1’;<br />

when "011" => LD_itv:=’0’<br />

when MSCNTV(2 downto 0)="111"<br />

else ’1’;<br />

when "100" => LD_itv:=’0’<br />

when MSCNTV(3 downto 0)="1111"<br />

else ’1’;<br />

when "101" => LD_itv:=’0’<br />

when MSCNTV(4 downto 0)="11111"<br />

else ’1’;<br />

when "110" => LD_itv:=’0’<br />

when MSCNTV(5 downto 0)="111111"<br />

else ’1’;<br />

when "111" => LD_itv:=’0’<br />

when MSCNTV(6 downto 0)="1111111"<br />

else ’1’;<br />

end case;<br />

-- test outputs<br />

DISCLK_ot :=DISCLK;<br />

MSC_ot :=MSC_itv;<br />

LD_ot :=LD_itv;<br />

RAS_ot :=RAS_itv;<br />

CAS_ot :=CAS_itv;<br />

MOE_ot :=MOE_itv;<br />

MWE_ot :=MWE_itv;<br />

MSF_ot :=MSF_itv;<br />

RCA_ot :=RCA_itv(8 downto 0);<br />

MSCNT_ot :=MSCNT mod 4096;<br />

TAPCNT_ot :=TAPCNT mod 2048;<br />

ROWCNT_ot :=ROWCNT mod 4096;<br />

CALC_NRL_ot :=CALC_NRL mod 256;<br />

CALC_NRH_ot :=CALC_NRH mod 256;<br />

SMR_req_ot :=SMR_request;<br />

SMR_high_ot :=SMR_high;<br />

-- for VRAM model control:<br />

Clk_Div:=’0’ when MSC_SFT=0<br />

and DISCLK=’0’ -- MSC = VClk<br />

and DISINC=’0’ -- disable 1st pulse<br />

else ’1’;<br />

T4 #1<br />

Abbildung 65: Speedchart-Diagramm VIDEO/RELOAD/RL MSC<br />

Anhang C.2<br />

Seite 98<br />

A: case MSC_SFT is<br />

when 0 => MSCNT:=0xFFF;<br />

when 1 => MSCNT:=((MSCNT + 1) mod 2) + 0xFFE;<br />

when 2 => MSCNT:=((MSCNT + 1) mod 4) + 0xFFC;<br />

when 3 => MSCNT:=((MSCNT + 1) mod 8) + 0xFF8;<br />

when 4 => MSCNT:=((MSCNT + 1) mod 16) + 0xFF0;<br />

when 5 => MSCNT:=((MSCNT + 1) mod 32) + 0xFE0;<br />

when 6 => MSCNT:=((MSCNT + 1) mod 64) + 0xFC0;<br />

when 7 => MSCNT:=((MSCNT + 1) mod 128) + 0xF80;<br />

when 8 => MSCNT:=((MSCNT + 1) mod 256) + 0xF00;<br />

when 9 => MSCNT:=((MSCNT + 1) mod 512) + 0xE00;<br />

when 10 => MSCNT:=((MSCNT + 1) mod 1024) + 0xC00;<br />

when 11 => MSCNT:=((MSCNT + 1) mod 2048) + 0x800;<br />

when others => MSCNT:=(MSCNT + 1) mod 4096;<br />

end case;<br />

if MSCNT=0xFFF and DISINC=’0’ then<br />

TAPCNT:=TAPCNT + 1 when TAPCNT/=0x7FF<br />

else 0x000 when SRL="11" -- 2048-2048<br />

else 0x400 when SRL="10" -- 2048-1024<br />

else 0x600 when SRL="01" -- 2048-512<br />

else 0x700; -- 2048-256<br />

end if;<br />

if MSCNT=0xFFF and DISINC=’0’ and CALC_NRH/=0<br />

and TAPCNT=0x7FF then<br />

SMR_request:=’1’;<br />

SMR_high:=’1’; -- high half SR data just finished<br />

end if;<br />

if MSCNT=0xFFF and DISINC=’0’ and CALC_NRL/=0<br />

and ((SRL="00" and TAPCNT=0x77F)<br />

or (SRL="01" and TAPCNT=0x6FF)<br />

or (SRL="10" and TAPCNT=0x5FF)<br />

or (SRL="11" and TAPCNT=0x3FF)) then<br />

SMR_request:=’1’;<br />

SMR_high:=’0’; -- low half SR data just finished<br />

end if;<br />

DISINC:=’0’;