DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

DIPLOMARBEIT - FG Mikroelektronik, TU Berlin

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Technische Universität <strong>Berlin</strong><br />

Institut für <strong>Mikroelektronik</strong><br />

Lukas Bauer<br />

Diplomarbeit<br />

Hochleistungs-Grafikprozessor in Speedchart-VHDL<br />

Abschnitt 4.5<br />

Seite 29<br />

26 8 7 0<br />

DPYNEXT:<br />

CALC ELL:<br />

15 8<br />

CALC ELL SFT<br />

7<br />

TAP (Start)<br />

0<br />

✜<br />

SUM TAP ELL:<br />

11 9 8 7<br />

TAP (Ende)<br />

0<br />

✜<br />

❭ +<br />

❄<br />

SUM TE A<br />

✛ ✑<br />

Anzahl der notwendigen Non-Split Reloads:<br />

CALC NRL := CALC ELL SFT + SUM TE A<br />

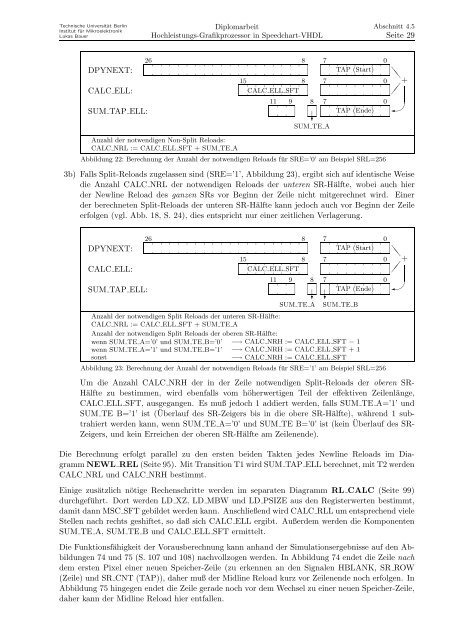

Abbildung 22: Berechnung der Anzahl der notwendigen Reloads für SRE=’0’ am Beispiel SRL=256<br />

3b) Falls Split-Reloads zugelassen sind (SRE=’1’, Abbildung 23), ergibt sich auf identische Weise<br />

die Anzahl CALC NRL der notwendigen Reloads der unteren SR-Hälfte, wobei auch hier<br />

der Newline Reload des ganzen SRs vor Beginn der Zeile nicht mitgerechnet wird. Einer<br />

der berechneten Split-Reloads der unteren SR-Hälfte kann jedoch auch vor Beginn der Zeile<br />

erfolgen (vgl. Abb. 18, S. 24), dies entspricht nur einer zeitlichen Verlagerung.<br />

26 8 7 0<br />

DPYNEXT:<br />

CALC ELL:<br />

15 8<br />

CALC ELL SFT<br />

7<br />

TAP (Start)<br />

0<br />

✜<br />

SUM TAP ELL:<br />

11 9 8 7<br />

TAP (Ende)<br />

0<br />

✜<br />

❭ +<br />

❄ ❄<br />

✛ ✑<br />

SUM TE A SUM TE B<br />

Anzahl der notwendigen Split Reloads der unteren SR-Hälfte:<br />

CALC NRL := CALC ELL SFT + SUM TE A<br />

Anzahl der notwendigen Split Reloads der oberen SR-Hälfte:<br />

wenn SUM TE A=’0’ und SUM TE B=’0’ −→ CALC NRH := CALC ELL SFT − 1<br />

wenn SUM TE A=’1’ und SUM TE B=’1’ −→ CALC NRH := CALC ELL SFT + 1<br />

sonst −→ CALC NRH := CALC ELL SFT<br />

Abbildung 23: Berechnung der Anzahl der notwendigen Reloads für SRE=’1’ am Beispiel SRL=256<br />

Um die Anzahl CALC NRH der in der Zeile notwendigen Split-Reloads der oberen SR-<br />

Hälfte zu bestimmen, wird ebenfalls vom höherwertigen Teil der effektiven Zeilenlänge,<br />

CALC ELL SFT, ausgegangen. Es muß jedoch 1 addiert werden, falls SUM TE A=’1’ und<br />

SUM TE B=’1’ ist (Überlauf des SR-Zeigers bis in die obere SR-Hälfte), während 1 subtrahiert<br />

werden kann, wenn SUM TE A=’0’ und SUM TE B=’0’ ist (kein Überlauf des SR-<br />

Zeigers, und kein Erreichen der oberen SR-Hälfte am Zeilenende).<br />

Die Berechnung erfolgt parallel zu den ersten beiden Takten jedes Newline Reloads im Diagramm<br />

NEWL REL (Seite 95). Mit Transition T1 wird SUM TAP ELL berechnet, mit T2 werden<br />

CALC NRL und CALC NRH bestimmt.<br />

Einige zusätzlich nötige Rechenschritte werden im separaten Diagramm RL CALC (Seite 99)<br />

durchgeführt. Dort werden LD XZ, LD MBW und LD PSIZE aus den Registerwerten bestimmt,<br />

damit dann MSC SFT gebildet werden kann. Anschließend wird CALC RLL um entsprechend viele<br />

Stellen nach rechts geshiftet, so daß sich CALC ELL ergibt. Außerdem werden die Komponenten<br />

SUM TE A, SUM TE B und CALC ELL SFT ermittelt.<br />

Die Funktionsfähigkeit der Vorausberechnung kann anhand der Simulationsergebnisse auf den Abbildungen<br />

74 und 75 (S. 107 und 108) nachvollzogen werden. In Abbildung 74 endet die Zeile nach<br />

dem ersten Pixel einer neuen Speicher-Zeile (zu erkennen an den Signalen HBLANK, SR ROW<br />

(Zeile) und SR CNT (TAP)), daher muß der Midline Reload kurz vor Zeilenende noch erfolgen. In<br />

Abbildung 75 hingegen endet die Zeile gerade noch vor dem Wechsel zu einer neuen Speicher-Zeile,<br />

daher kann der Midline Reload hier entfallen.