Diplomarbeit - Eingebettete Systeme - Technische Universität ...

Diplomarbeit - Eingebettete Systeme - Technische Universität ...

Diplomarbeit - Eingebettete Systeme - Technische Universität ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

2.7 Grundlagen der Phasendetektion<br />

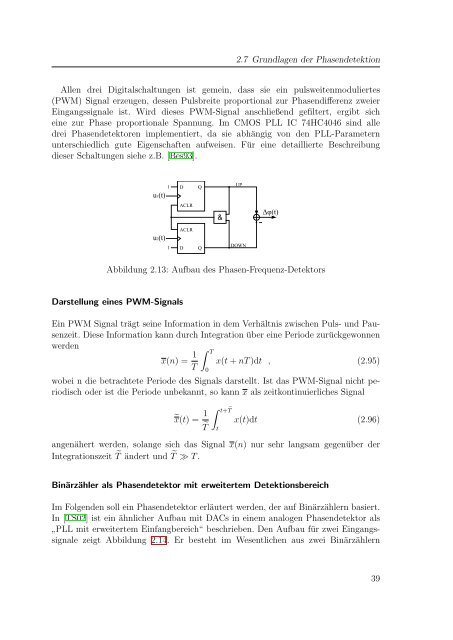

Allen drei Digitalschaltungen ist gemein, dass sie ein pulsweitenmoduliertes<br />

(PWM) Signal erzeugen, dessen Pulsbreite proportional zur Phasendifferenz zweier<br />

Eingangssignale ist. Wird dieses PWM-Signal anschließend gefiltert, ergibt sich<br />

eine zur Phase proportionale Spannung. Im CMOS PLL IC 74HC4046 sind alle<br />

drei Phasendetektoren implementiert, da sie abhängig von den PLL-Parametern<br />

unterschiedlich gute Eigenschaften aufweisen. Für eine detaillierte Beschreibung<br />

dieser Schaltungen siehe z.B. [Bes93].<br />

Abbildung 2.13: Aufbau des Phasen-Frequenz-Detektors<br />

Darstellung eines PWM-Signals<br />

Ein PWM Signal trägt seine Information in dem Verhältnis zwischen Puls- und Pausenzeit.<br />

Diese Information kann durch Integration über eine Periode zurückgewonnen<br />

werden<br />

x(n) = 1<br />

T<br />

� T<br />

0<br />

x(t + nT )dt , (2.95)<br />

wobei n die betrachtete Periode des Signals darstellt. Ist das PWM-Signal nicht periodisch<br />

oder ist die Periode unbekannt, so kann x als zeitkontinuierliches Signal<br />

�x(t) = 1<br />

�T<br />

� t+ � T<br />

t<br />

x(t)dt (2.96)<br />

angenähert werden, solange sich das Signal x(n) nur sehr langsam gegenüber der<br />

Integrationszeit � T ändert und � T ≫ T .<br />

Binärzähler als Phasendetektor mit erweitertem Detektionsbereich<br />

Im Folgenden soll ein Phasendetektor erläutert werden, der auf Binärzählern basiert.<br />

In [TS02] ist ein ähnlicher Aufbau mit DACs in einem analogen Phasendetektor als<br />

” PLL mit erweitertem Einfangbereich“ beschrieben. Den Aufbau für zwei Eingangssignale<br />

zeigt Abbildung 2.14. Er besteht im Wesentlichen aus zwei Binärzählern<br />

39