TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

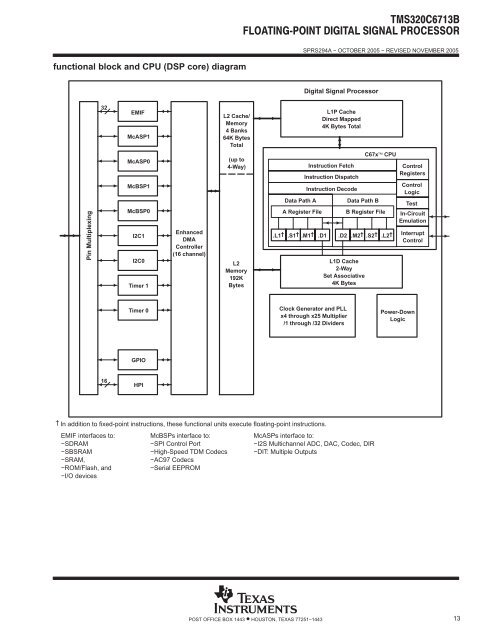

functional block and CPU (DSP core) diagram<br />

SPRS294A − OCTOBER 2005 − REVISED NOVEMBER 2005<br />

<strong>Digital</strong> <strong>Signal</strong> <strong>Processor</strong><br />

Pin Multiplexing<br />

32<br />

EMIF<br />

McASP1<br />

McASP0<br />

McBSP1<br />

McBSP0<br />

I2C1<br />

I2C0<br />

Timer 1<br />

Enhanced<br />

DMA<br />

Controller<br />

(16 channel)<br />

L2 Cache/<br />

Memory<br />

4 Banks<br />

64K Bytes<br />

Total<br />

(up to<br />

4-Way)<br />

L2<br />

Memory<br />

192K<br />

Bytes<br />

L1P Cache<br />

Direct Mapped<br />

4K Bytes Total<br />

Instruction Fetch<br />

Instruction Dispatch<br />

C67x CPU<br />

Instruction Decode<br />

Data Path A<br />

Data Path B<br />

A Register File B Register File<br />

.L1 † .S1 † .M1 † .D1 .D2 .M2 † .S2 † .L2 †<br />

L1D Cache<br />

2-Way<br />

Set Associative<br />

4K Bytes<br />

Control<br />

Registers<br />

Control<br />

Logic<br />

Test<br />

In-Circuit<br />

Emulation<br />

Interrupt<br />

Control<br />

Timer 0<br />

Clock Generator and PLL<br />

x4 through x25 Multiplier<br />

/1 through /32 Dividers<br />

Power-Down<br />

Logic<br />

GPIO<br />

16<br />

HPI<br />

† In addition to fixed-point instructions, these functional units execute floating-point instructions.<br />

EMIF interfaces to:<br />

−SDRAM<br />

−SBSRAM<br />

−SRAM,<br />

−ROM/Flash, and<br />

−I/O devices<br />

McBSPs interface to:<br />

−SPI Control Port<br />

−High-Speed TDM Codecs<br />

−AC97 Codecs<br />

−Serial EEPROM<br />

McASPs interface to:<br />

−I2S Multichannel ADC, DAC, Codec, DIR<br />

−DIT: Multiple Outputs<br />

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443<br />

13