TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

SPRS294A − OCTOBER 2005 − REVISED NOVEMBER 2005<br />

DSP<br />

INTERRUPT<br />

NUMBER<br />

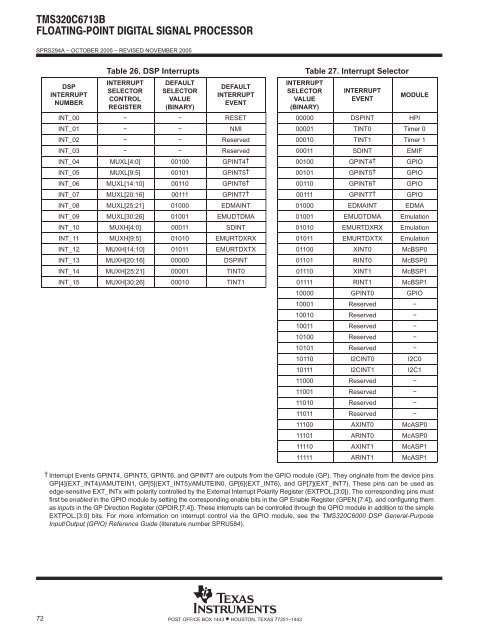

Table 26. DSP Interrupts<br />

INTERRUPT<br />

SELECTOR<br />

CONTROL<br />

REGISTER<br />

DEFAULT<br />

SELECTOR<br />

VALUE<br />

(BINARY)<br />

DEFAULT<br />

INTERRUPT<br />

EVENT<br />

INTERRUPT<br />

SELECTOR<br />

VALUE<br />

(BINARY)<br />

Table 27. Interrupt Selector<br />

INTERRUPT<br />

EVENT<br />

MODULE<br />

INT_00 − − RESET 00000 DSPINT HPI<br />

INT_01 − − NMI 00001 TINT0 Timer 0<br />

INT_02 − − Reserved 00010 TINT1 Timer 1<br />

INT_03 − − Reserved 00011 SDINT EMIF<br />

INT_04 MUXL[4:0] 00100 GPINT4† 00100 GPINT4† GPIO<br />

INT_05 MUXL[9:5] 00101 GPINT5† 00101 GPINT5† GPIO<br />

INT_06 MUXL[14:10] 00110 GPINT6† 00110 GPINT6† GPIO<br />

INT_07 MUXL[20:16] 00111 GPINT7† 00111 GPINT7† GPIO<br />

INT_08 MUXL[25:21] 01000 EDMAINT 01000 EDMAINT EDMA<br />

INT_09 MUXL[30:26] 01001 EMUDTDMA 01001 EMUDTDMA Emulation<br />

INT_10 MUXH[4:0] 00011 SDINT 01010 EMURTDXRX Emulation<br />

INT_11 MUXH[9:5] 01010 EMURTDXRX 01011 EMURTDXTX Emulation<br />

INT_12 MUXH[14:10] 01011 EMURTDXTX 01100 XINT0 McBSP0<br />

INT_13 MUXH[20:16] 00000 DSPINT 01101 RINT0 McBSP0<br />

INT_14 MUXH[25:21] 00001 TINT0 01110 XINT1 McBSP1<br />

INT_15 MUXH[30:26] 00010 TINT1 01111 RINT1 McBSP1<br />

10000 GPINT0 GPIO<br />

10001 Reserved −<br />

10010 Reserved −<br />

10011 Reserved −<br />

10100 Reserved −<br />

10101 Reserved −<br />

10110 I2CINT0 I2C0<br />

10111 I2CINT1 I2C1<br />

11000 Reserved −<br />

11001 Reserved −<br />

11010 Reserved −<br />

11011 Reserved −<br />

11100 AXINT0 McASP0<br />

11101 ARINT0 McASP0<br />

11110 AXINT1 McASP1<br />

11111 ARINT1 McASP1<br />

† Interrupt Events GPINT4, GPINT5, GPINT6, and GPINT7 are outputs from the GPIO module (GP). They originate from the device pins<br />

GP[4](EXT_INT4)/AMUTEIN1, GP[5](EXT_INT5)/AMUTEIN0, GP[6](EXT_INT6), and GP[7](EXT_INT7). These pins can be used as<br />

edge-sensitive EXT_INTx with polarity controlled by the External Interrupt Polarity Register (EXTPOL.[3:0]). The corresponding pins must<br />

first be enabled in the GPIO module by setting the corresponding enable bits in the GP Enable Register (GPEN.[7:4]), and configuring them<br />

as inputs in the GP Direction Register (GPDIR.[7:4]). These interrupts can be controlled through the GPIO module in addition to the simple<br />

EXTPOL.[3:0] bits. For more information on interrupt control via the GPIO module, see the TMS320C6000 DSP General-Purpose<br />

Input/Output (GPIO) Reference Guide (literature number SPRU584).<br />

72 POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443