TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

SPRS294A − OCTOBER 2005 − REVISED NOVEMBER 2005<br />

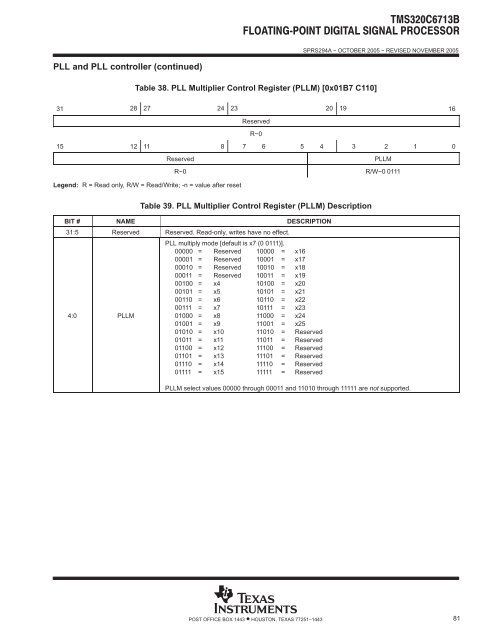

PLL and PLL controller (continued)<br />

Table 38. PLL Multiplier Control Register (PLLM) [0x01B7 C110]<br />

31 28 27 24 23 20 19 16<br />

Reserved<br />

R−0<br />

15 12 11 8 7 6 5 4 3 2 1 0<br />

Reserved<br />

PLLM<br />

R−0 R/W−0 0111<br />

Legend: R = Read only, R/W = Read/Write; -n = value after reset<br />

Table 39. PLL Multiplier Control Register (PLLM) Description<br />

BIT # NAME DESCRIPTION<br />

31:5 Reserved Reserved. Read-only, writes have no effect.<br />

4:0 PLLM<br />

PLL multiply mode [default is x7 (0 0111)].<br />

00000 = Reserved 10000 = x16<br />

00001 = Reserved 10001 = x17<br />

00010 = Reserved 10010 = x18<br />

00011 = Reserved 10011 = x19<br />

00100 = x4 10100 = x20<br />

00101 = x5 10101 = x21<br />

00110 = x6 10110 = x22<br />

00111 = x7 10111 = x23<br />

01000 = x8 11000 = x24<br />

01001 = x9 11001 = x25<br />

01010 = x10 11010 = Reserved<br />

01011 = x11 11011 = Reserved<br />

01100 = x12 11100 = Reserved<br />

01101 = x13 11101 = Reserved<br />

01110 = x14 11110 = Reserved<br />

01111 = x15 11111 = Reserved<br />

PLLM select values 00000 through 00011 and 11010 through 11111 are not supported.<br />

POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443<br />

81