TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

TMS320C6713B Floating-Point Digital Signal Processor (Rev. A)

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

SPRS294 − OCTOBER 2005<br />

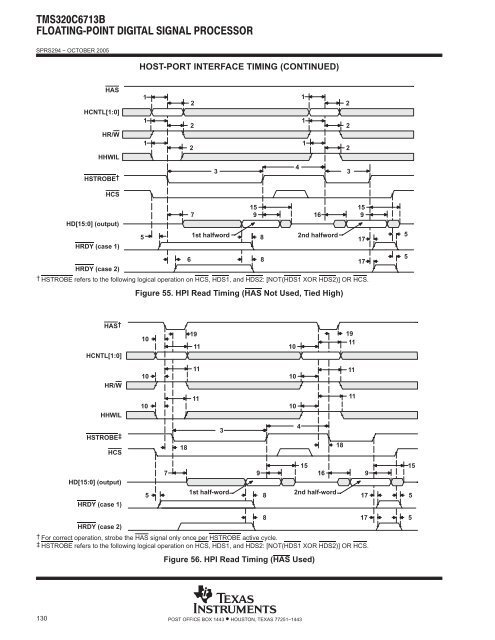

HOST-PORT INTERFACE TIMING (CONTINUED)<br />

HAS<br />

HCNTL[1:0]<br />

HR/W<br />

HHWIL<br />

HSTROBE†<br />

1<br />

1<br />

1<br />

2<br />

2<br />

2<br />

3<br />

1<br />

1<br />

1<br />

4<br />

2<br />

2<br />

2<br />

3<br />

HCS<br />

HD[15:0] (output)<br />

HRDY (case 1)<br />

5<br />

7<br />

1st halfword<br />

15<br />

9<br />

8<br />

16<br />

2nd halfword<br />

6<br />

8<br />

17<br />

HRDY (case 2)<br />

† HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.<br />

15<br />

9<br />

17<br />

5<br />

5<br />

Figure 55. HPI Read Timing (HAS Not Used, Tied High)<br />

HAS†<br />

HCNTL[1:0]<br />

10<br />

19 19<br />

11<br />

10<br />

11<br />

HR/W<br />

10<br />

11<br />

10<br />

11<br />

HHWIL<br />

10<br />

11<br />

10<br />

11<br />

HSTROBE‡<br />

HCS<br />

18<br />

3<br />

4<br />

18<br />

HD[15:0] (output)<br />

HRDY (case 1)<br />

5<br />

7<br />

1st half-word<br />

9<br />

8<br />

15<br />

16<br />

2nd half-word<br />

9<br />

17<br />

15<br />

5<br />

HRDY (case 2)<br />

† For correct operation, strobe the HAS signal only once per HSTROBE active cycle.<br />

‡ HSTROBE refers to the following logical operation on HCS, HDS1, and HDS2: [NOT(HDS1 XOR HDS2)] OR HCS.<br />

8<br />

17<br />

5<br />

Figure 56. HPI Read Timing (HAS Used)<br />

130 POST OFFICE BOX 1443 • HOUSTON, TEXAS 77251−1443