Entwicklung einer Nanotechnologie-Plattform für die ... - JuSER

Entwicklung einer Nanotechnologie-Plattform für die ... - JuSER

Entwicklung einer Nanotechnologie-Plattform für die ... - JuSER

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

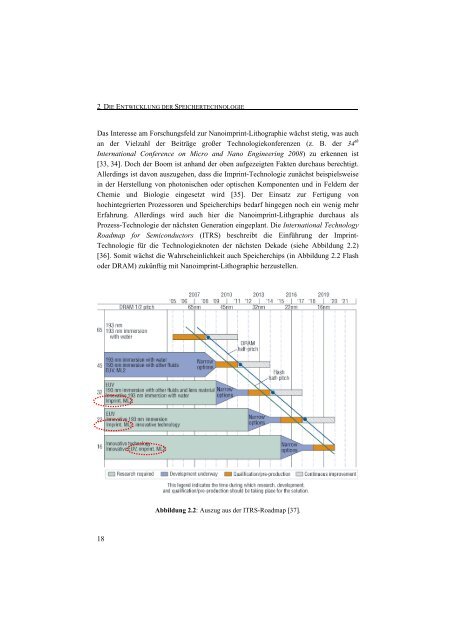

2 DIE ENTWICKLUNG DER SPEICHERTECHNOLOGIE<br />

Das Interesse am Forschungsfeld zur Nanoimprint-Lithographie wächst stetig, was auch<br />

an der Vielzahl der Beiträge großer Technologiekonferenzen (z. B. der 34 th<br />

International Conference on Micro and Nano Engineering 2008) zu erkennen ist<br />

[33, 34]. Doch der Boom ist anhand der oben aufgezeigten Fakten durchaus berechtigt.<br />

Allerdings ist davon auszugehen, dass <strong>die</strong> Imprint-Technologie zunächst beispielsweise<br />

in der Herstellung von photonischen oder optischen Komponenten und in Feldern der<br />

Chemie und Biologie eingesetzt wird [35]. Der Einsatz zur Fertigung von<br />

hochintegrierten Prozessoren und Speicherchips bedarf hingegen noch ein wenig mehr<br />

Erfahrung. Allerdings wird auch hier <strong>die</strong> Nanoimprint-Lithgraphie durchaus als<br />

Prozess-Technologie der nächsten Generation eingeplant. Die International Technology<br />

Roadmap for Semiconductors (ITRS) beschreibt <strong>die</strong> Einführung der Imprint-<br />

Technologie <strong>für</strong> <strong>die</strong> Technologieknoten der nächsten Dekade (siehe Abbildung 2.2)<br />

[36]. Somit wächst <strong>die</strong> Wahrscheinlichkeit auch Speicherchips (in Abbildung 2.2 Flash<br />

oder DRAM) zukünftig mit Nanoimprint-Lithographie herzustellen.<br />

Abbildung 2.2: Auszug aus der ITRS-Roadmap [37].<br />

18