- Page 1 and 2:

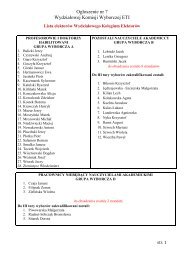

POLITECHNIKA GDAŃSKA Pakiet inform

- Page 3 and 4:

1. Opis Wydziału Wydział Elektron

- Page 5 and 6:

1.2. Władze Wydziału Dziekan prof

- Page 7 and 8:

Katedra Systemów Automatyki Kierow

- Page 9 and 10:

Na program studiów na każdym stop

- Page 11 and 12:

Ogólny schemat studiowania na stud

- Page 13 and 14:

1.5.6. Skala ocen Zgodnie z „Regu

- Page 15 and 16:

Semestr 3 kierunek AUTOMATYKA i ROB

- Page 17 and 18:

Semestr 6 - strumień: Systemy decy

- Page 19 and 20:

Semestr 3 kierunek ELEKTRONIKA I TE

- Page 21 and 22:

Semestr 6 - strumień: Elektronika

- Page 23 and 24:

Profil dyplomowania: Systemy mikroe

- Page 25 and 26:

2.3. Informatyka 2.3.1. Rdzeń i st

- Page 27 and 28:

Semestr 6 - strumień: Aplikacje ki

- Page 29 and 30:

Profil dyplomowania: Systemy geoinf

- Page 31 and 32:

Semestr 3 kierunek AUTOMATYKA i ROB

- Page 33 and 34:

3.2.2. Specjalności Specjalność:

- Page 35 and 36:

Specjalność: Sieci i systemy tele

- Page 37 and 38:

3.3. Informatyka 3.3.1. Rdzeń Seme

- Page 39 and 40:

Specjalność: Inżynieria systemó

- Page 41 and 42:

4.1. Przedmioty ogólne, podstawowe

- Page 43 and 44:

Nazwa przedmiotu Algorytmy i strukt

- Page 45 and 46:

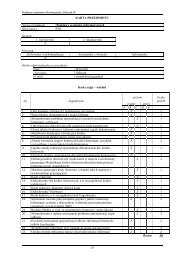

Karta zajęć - projekt Lp. Zagadni

- Page 47 and 48:

Karta zajęć - laboratorium poziom

- Page 49 and 50:

33. Rozwiązywanie dowolnych układ

- Page 51 and 52:

21. Macierze. Działania na macierz

- Page 53 and 54:

3. Twierdzenie Stokesa i twierdzeni

- Page 55 and 56:

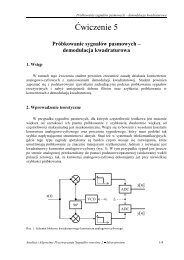

22. Detektory amplitudy, częstotli

- Page 57 and 58:

22. Detektory amplitudy, częstotli

- Page 59 and 60:

Lp. Zagadnienie Karta zajęć - pro

- Page 61 and 62:

Karta zajęć - projekt Lp. Zagadni

- Page 63 and 64:

Karta przedmiotu - Systemy wbudowan

- Page 65 and 66:

18. Usługi systemowe i ich wywoły

- Page 67 and 68:

5. Kodowanie bitowe programów X 2

- Page 69 and 70:

22. Architektura komputerów w stan

- Page 71 and 72:

21. Systemy wieloprocesorowe z pami

- Page 73 and 74:

21. UDDI - modelowanie związków p

- Page 75 and 76:

Nazwa przedmiotu Bazy danych Skrót

- Page 77 and 78:

Nazwa przedmiotu Bazy danych Skrót

- Page 79 and 80:

Nazwa przedmiotu Bazy wiedzy Skrót

- Page 81 and 82:

KARTA PRZEDMIOTU Nazwa przedmiotu B

- Page 83 and 84:

KARTA PRZEDMIOTU Nazwa przedmiotu B

- Page 85 and 86:

Nazwa przedmiotu Eksploracja danych

- Page 87 and 88:

Nazwa przedmiotu Elektrodynamika Sk

- Page 89 and 90:

Nazwa przedmiotu Elementy elektroni

- Page 91 and 92:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 93 and 94:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 95 and 96:

Lp. Zagadnienie Karta zajęć - lab

- Page 97 and 98:

głosowego. Filtry kratowe - właś

- Page 99 and 100:

19. ciepło dostarczone. Entropia a

- Page 101 and 102:

Faraday’a. 17. Kolokwium zaliczen

- Page 103 and 104:

Lp. Zagadnienie poziom liczba godzi

- Page 105 and 106:

Tematy ćwiczeń 1. Wyznaczanie cza

- Page 107 and 108:

22. zbioru, zbiory w sobie gęste,

- Page 109 and 110:

84. Kompresja bezstratna metodami s

- Page 111 and 112:

Karta przedmiotu - Humanistyka dla

- Page 113 and 114:

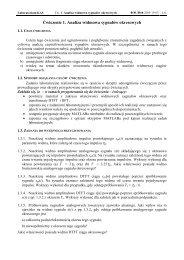

6. Analiza efektów załadowania hu

- Page 115 and 116:

12. Uczenie maszynowe VI - Porówna

- Page 117 and 118:

19. Przegląd standardów interfejs

- Page 119 and 120:

21. UDDI - modelowanie związków p

- Page 121 and 122:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 123 and 124:

Nazwa przedmiotu Inżynieria mikrof

- Page 125 and 126:

Karta przedmiotu - Inżynieria opro

- Page 127 and 128:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 129 and 130:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 131 and 132:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 133 and 134:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 135 and 136:

Nazwa przedmiotu Jakość oprogramo

- Page 137 and 138:

Nazwa przedmiotu Języki projektowa

- Page 139 and 140:

KARTA PRZEDMIOTU Nazwa przedmiotu J

- Page 141 and 142:

NICONET, SLICOT oraz NETLIB. Lp. Za

- Page 143 and 144:

4. Języki znaczników HTML i XHTML

- Page 145 and 146:

Lp. Zagadnienie poziom liczba godzi

- Page 147 and 148:

25. Badania odporności i emisyjno

- Page 149 and 150:

KARTA PRZEDMIOTU Nazwa przedmiotu K

- Page 151 and 152:

KARTA PRZEDMIOTU Nazwa przedmiotu K

- Page 153 and 154:

Nazwa przedmiotu Konstrukcja kompil

- Page 155 and 156:

Nazwa przedmiotu Konwertery mocy Sk

- Page 157 and 158:

KARTA PRZEDMIOTU Nazwa przedmiotu L

- Page 159 and 160:

Nazwa przedmiotu Matematyka dyskret

- Page 161 and 162:

Nazwa przedmiotu Matematyka dyskret

- Page 163 and 164:

13. Czujniki pomiaru konta X 0,5 14

- Page 165 and 166:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 167 and 168:

13. Opracowanie obiektowej wersji p

- Page 169 and 170:

Lp. Zagadnienie Karta zajęć - lab

- Page 171 and 172:

algorytmów niestabilnych numeryczn

- Page 173 and 174:

Karta zajęć - laboratorium Poziom

- Page 175 and 176:

14. Entropia zmiennej losowej: defi

- Page 177 and 178:

24. rozmieszczania elementów na p

- Page 179 and 180:

27. Wydzielanie segmentów: metody

- Page 181 and 182:

2. Projekt i realizacja statycznej

- Page 183 and 184:

23. Obróbka i wizualizacja danych

- Page 185 and 186:

23. Wewnętrzne komparatory analogo

- Page 187 and 188:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 189 and 190:

KARTA PRZEDMIOTU Nazwa przedmiotu M

- Page 191 and 192:

4. Projekt i implementacja programu

- Page 193 and 194:

3. Przetwarzanie i edycja wideo. Mo

- Page 195 and 196:

17. Testowanie jakości aplikacji p

- Page 197 and 198:

19. stanie nieustalonym. Zastępcze

- Page 199 and 200:

częstotliwościowe filtru idealneg

- Page 201 and 202:

19. Zastępcze schematy operatorowe

- Page 203 and 204:

dolnoprzepustowe. Asymptotyczne cha

- Page 205 and 206:

Karta zajęć - laboratorium poziom

- Page 207 and 208:

20. Zarządzanie procesami na pozio

- Page 209 and 210:

31. Sensoryka optyczna X 1 32. Tren

- Page 211 and 212:

25. Elementy architektury x86-32 i

- Page 213 and 214:

wykorzystaniem programowania liniow

- Page 215 and 216:

Nazwa przedmiotu Platformy technolo

- Page 217 and 218:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 219 and 220:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 221 and 222:

Nazwa przedmiotu Podstawy automatyk

- Page 223 and 224:

częstotliwościowe: regulatory pro

- Page 225 and 226:

Karta zajęć - projekt Lp. Zagadni

- Page 227 and 228:

przedstawiciela inwestora (venture

- Page 229 and 230:

17. niepewność standardowa i rozs

- Page 231 and 232:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 233 and 234:

Nazwa przedmiotu Podstawy mikroelek

- Page 235 and 236:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 237 and 238:

29. Przykłady chwytaków i narzęd

- Page 239 and 240:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 241 and 242:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 243 and 244:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 245 and 246:

Nazwa przedmiotu Podstawy telekomun

- Page 247 and 248:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 249 and 250:

Nazwa przedmiotu Praktyka programow

- Page 251 and 252:

Nazwa przedmiotu Procesory sygnało

- Page 253 and 254:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 255 and 256:

KARTA PRZEDMIOTU Nazwa przedmiotu P

- Page 257 and 258:

Lp. Zagadnienie Karta zajęć - pro

- Page 259 and 260:

19. Realizacja współbieżności p

- Page 261 and 262:

Lp. Zagadnienie Karta zajęć - lab

- Page 263 and 264:

10. Specyfika topologii sieci w sys

- Page 265 and 266:

19. Elementy grafiki komputerowej i

- Page 267 and 268:

24. miar i metryk Mechanizmy komuni

- Page 269 and 270:

Karta zajęć - ćwiczenia Razem 30

- Page 271 and 272:

Karta zajęć - ćwiczenia Razem 30

- Page 273 and 274:

Lp. Zagadnienie Karta zajęć - lab

- Page 275 and 276:

20. Ciągi Markowa, znaczenie dla a

- Page 277 and 278:

KARTA PRZEDMIOTU Nazwa przedmiotu R

- Page 279 and 280:

Karta zajęć - laboratorium Lp. Za

- Page 281 and 282:

Lp. Zagadnienie Karta zajęć - lab

- Page 283 and 284:

Karta zajęć - laboratorium poziom

- Page 285 and 286:

30. ARP, ICMP, fragmentacja i defra

- Page 287 and 288:

przeciwdziałania przeciążeniom 2

- Page 289 and 290:

30. Wsparcie mobilności w sieciach

- Page 291 and 292:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 293 and 294:

nieliniowego obiektu autonomicznego

- Page 295 and 296:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 297 and 298:

Karta zajęć - laboratorium poziom

- Page 299 and 300:

3. Eksperymentowanie z sortowaniem

- Page 301 and 302:

jakość. 14. Porównanie charakter

- Page 303 and 304:

Nazwa przedmiotu Systemy echolokacy

- Page 305 and 306:

Nazwa przedmiotu Systemy i architek

- Page 307 and 308:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 309 and 310:

2. Zasięg transmisji w trakcie opt

- Page 311 and 312:

14. Prezentacja dźwięku i obrazu.

- Page 313 and 314:

Karta zajęć - laboratorium Lp. Za

- Page 315 and 316:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 317 and 318:

Nazwa przedmiotu Systemy operacyjne

- Page 319 and 320:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 321 and 322:

Nazwa przedmiotu Systemy telekomuni

- Page 323 and 324:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 325 and 326:

KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 327 and 328:

Nazwa przedmiotu Sztuczna inteligen

- Page 329 and 330:

Nazwa przedmiotu Technika antenowa

- Page 331 and 332:

zastępcze, zasada działania, meto

- Page 333 and 334:

Nazwa przedmiotu Technika bezprzewo

- Page 335 and 336:

Nazwa przedmiotu Technika bezprzewo

- Page 337 and 338:

Nazwa przedmiotu Technika cyfrowa S

- Page 339 and 340:

13. Przykłady syntezy układów ko

- Page 341 and 342:

Nazwa przedmiotu Technika laserowa

- Page 343 and 344:

KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 345 and 346:

KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 347 and 348:

KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 349 and 350:

siatki Bragga, ich rodzaje, charakt

- Page 351 and 352:

Karta zajęć - laboratorium poziom

- Page 353 and 354:

17. Wielkości transmisyjne, parame

- Page 355 and 356:

23. Grafika rastrowa - definicja, p

- Page 357 and 358:

Lp. Zagadnienie Karta zajęć - lab

- Page 359 and 360:

Karta zajęć - laboratorium poziom

- Page 361 and 362:

sposoby wyzwalania. Projektowania l

- Page 363 and 364:

Nazwa przedmiotu Układy logiczne S

- Page 365 and 366:

Lp. Zagadnienie Karta zajęć - lab

- Page 367 and 368:

systemów wielodostępowych. 4. Wyk

- Page 369 and 370:

1. Łączenie uczestników sceny dy

- Page 371 and 372:

18. Szczególne typy form graficzny

- Page 373 and 374:

KARTA PRZEDMIOTU Nazwa przedmiotu W

- Page 375 and 376:

KARTA PRZEDMIOTU Nazwa przedmiotu W

- Page 377 and 378:

KARTA PRZEDMIOTU Nazwa przedmiotu W

- Page 379 and 380:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 381 and 382:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 383 and 384:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 385 and 386:

KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 387 and 388:

4.2. Przedmioty profilujące KARTA

- Page 389 and 390:

Nazwa przedmiotu Akustyka środowis

- Page 391 and 392:

Nazwa przedmiotu Algorytmy genetycz

- Page 393 and 394:

Nazwa przedmiotu Analogowe układy

- Page 395 and 396:

Nazwa przedmiotu Animacja komputero

- Page 397 and 398:

KARTA PRZEDMIOTU Nazwa przedmiotu A

- Page 399 and 400:

Nazwa przedmiotu Aplikacje baz dany

- Page 401 and 402:

KARTA PRZEDMIOTU Nazwa przedmiotu A

- Page 403 and 404:

Nazwa przedmiotu Biopomiary Skrót

- Page 405 and 406:

KARTA PRZEDMIOTU Nazwa przedmiotu B

- Page 407 and 408:

KARTA PRZEDMIOTU Nazwa przedmiotu C

- Page 409 and 410:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 411 and 412:

KARTA PRZEDMIOTU Nazwa przedmiotu E

- Page 413 and 414:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 415 and 416:

KARTA PRZEDMIOTU Nazwa przedmiotu I

- Page 417 and 418:

Lp. Zagadnienie Karta zajęć - lab

- Page 419 and 420:

Opracowanie projektu interfejsu uż

- Page 421 and 422:

3. Analiza częstotliwościowa sygn

- Page 423 and 424:

Lp. Zagadnienie Karta zajęć - pro

- Page 425 and 426:

Lp. Zagadnienie Karta zajęć - pro

- Page 427 and 428:

2. Omówienie tematów projektów,

- Page 429 and 430:

Karta zajęć - laboratorium poziom

- Page 431 and 432:

5. Badanie przenośnej radiostacji

- Page 433 and 434:

programowego). 6. Projekt własnego

- Page 435 and 436:

Karta zajęć - laboratorium poziom

- Page 437 and 438:

22. Przykłady oraz dobór konstela

- Page 439 and 440:

30. Wzorce projektowe warstwy preze

- Page 441 and 442:

31. Metoda Lee zapisu amplitud zesp

- Page 443 and 444:

KARTA PRZEDMIOTU Nazwa przedmiotu O

- Page 445 and 446:

zasady. X X 2 2. Wyznaczanie strefy

- Page 447 and 448:

2. Bezkontaktowy pomiar temperatury

- Page 449 and 450:

23. Tworzenie aplikacji przemysłow

- Page 451 and 452:

29. Subwoofery. X 0,33 30. Kolumny

- Page 453 and 454:

2. Komunikacja pomiędzy systemami

- Page 455 and 456:

2. Modulator/demodulator sygnału G

- Page 457 and 458:

Lp. Zagadnienie Karta zajęć - pro

- Page 459 and 460:

Lp. Zagadnienie Karta zajęć - lab

- Page 461 and 462:

46. Tryby pracy jednostki ALU/MACC

- Page 463 and 464:

4. Próbkowanie sygnałów pasmowyc

- Page 465 and 466:

Karta zajęć - laboratorium poziom

- Page 467 and 468:

Lp. Zagadnienie Karta zajęć - lab

- Page 469 and 470:

Lp. Zagadnienie Karta zajęć - lab

- Page 471 and 472:

urządzenia przenośne 34. Testowan

- Page 473 and 474:

5. Java: platformówka X 2 6. Java:

- Page 475 and 476:

17. Przykłady rozwiązań urządze

- Page 477 and 478:

6. Prezentacja zrealizowanego oprog

- Page 479 and 480:

Karta zajęć - laboratorium poziom

- Page 481 and 482:

4. Wykonanie i weryfikacja poprawno

- Page 483 and 484:

5. Układy dopasowujące w zakresie

- Page 485 and 486: Lp. Zagadnienie Karta zajęć - pro

- Page 487 and 488: Lp. Zagadnienie Karta zajęć - lab

- Page 489 and 490: KARTA PRZEDMIOTU Nazwa przedmiotu R

- Page 491 and 492: 20. Mapy otoczenia (opis rastrowy,

- Page 493 and 494: 29. JDBC X 0,66 30. Idea Java Beans

- Page 495 and 496: 18. Usługi kontrolowanej i gwarant

- Page 497 and 498: KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 499 and 500: Karta zajęć - projekt poziom licz

- Page 501 and 502: Karta zajęć - laboratorium poziom

- Page 503 and 504: 2. Analiza projektowa i projekt sys

- Page 505 and 506: KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 507 and 508: Nazwa przedmiotu Systemy nawigacyjn

- Page 509 and 510: KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 511 and 512: KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 513 and 514: Nazwa przedmiotu Systemy wspierania

- Page 515 and 516: KARTA PRZEDMIOTU Nazwa przedmiotu S

- Page 517 and 518: KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 519 and 520: Nazwa przedmiotu Techniki obrazowan

- Page 521 and 522: Nazwa przedmiotu Technologia studyj

- Page 523 and 524: KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 525 and 526: KARTA PRZEDMIOTU Nazwa przedmiotu T

- Page 527 and 528: KARTA PRZEDMIOTU Nazwa przedmiotu U

- Page 529 and 530: KARTA PRZEDMIOTU Nazwa przedmiotu W

- Page 531 and 532: KARTA PRZEDMIOTU Nazwa przedmiotu Z

- Page 533 and 534: Nazwa przedmiotu Zarządzanie sieci

- Page 535: 4. Konfigurowanie środowiska rozpr

![Wersja pełna [8,55 MB] - Wydział Elektroniki, Telekomunikacji i ...](https://img.yumpu.com/19534759/536/500x640/wersja-pelna-855-mb-wydzial-elektroniki-telekomunikacji-i-.jpg)

![Wersja pełna [11,39 MB] - Wydział Elektroniki, Telekomunikacji i ...](https://img.yumpu.com/19534885/1/184x260/wersja-pelna-1139-mb-wydzial-elektroniki-telekomunikacji-i-.jpg?quality=85)

![Wersja pełna [11,39 MB] - Wydział Elektroniki, Telekomunikacji i ...](https://img.yumpu.com/19534883/1/184x260/wersja-pelna-1139-mb-wydzial-elektroniki-telekomunikacji-i-.jpg?quality=85)

![Wersja pełna [10,99 MB] - Wydział Elektroniki, Telekomunikacji i ...](https://img.yumpu.com/19534878/1/184x260/wersja-pelna-1099-mb-wydzial-elektroniki-telekomunikacji-i-.jpg?quality=85)

![2cos( ][ n FF nx ⋅⋅⋅ = ) 2cos( ])[ 1(][ n FF nxm nx ⋅⋅⋅ ⋅ ⋅+= ) 2cos ...](https://img.yumpu.com/19534764/1/184x260/2cos-n-ff-nx-2cos-1-n-ff-nxm-nx-2cos-.jpg?quality=85)