- Page 2 and 3:

M. Nastasi J.W. MayerIon Implantati

- Page 4 and 5:

To our loved ones

- Page 7 and 8:

xContents4 Cross-Section ..........

- Page 10 and 11:

Contentsxiii14.3.2 Punch-Through St

- Page 12 and 13:

2 1 General Features and Fundamenta

- Page 14 and 15:

4 1 General Features and Fundamenta

- Page 16 and 17:

6 1 General Features and Fundamenta

- Page 18 and 19:

8 1 General Features and Fundamenta

- Page 20 and 21:

10 1 General Features and Fundament

- Page 22 and 23:

12 2 Particle InteractionsThe restr

- Page 24 and 25:

142 Particle Interactions(a)V(r)r 0

- Page 26 and 27:

162 Particle InteractionsHowever, a

- Page 28 and 29:

182 Particle Interactionswhere the

- Page 30 and 31:

202 Particle Interactionsa0.8853a0L

- Page 33 and 34:

3 Dynamics of Binary Elastic Collis

- Page 35 and 36:

3.3 Kinematics of Elastic Collision

- Page 37 and 38:

3.4 Center-of-Mass Coordinates 27Fi

- Page 39 and 40:

3.4 Center-of-Mass Coordinates 29an

- Page 41 and 42:

3.5 Motion under a Central Force 31

- Page 43 and 44:

3.5 Motion under a Central Force 33

- Page 45 and 46:

Problems 35The reduced energy for 1

- Page 47 and 48:

4 Cross-Section4.1 IntroductionIn C

- Page 49 and 50:

4.2 Scattering Cross-Section 39unit

- Page 51 and 52:

4.2 Scattering Cross-Section 41Rdθ

- Page 53 and 54:

4.3 Energy-Transfer Cross-Section 4

- Page 55 and 56:

4.4 Approximation to the Energy-Tra

- Page 57 and 58:

Problems 47ReferencesNastasi, M., M

- Page 59 and 60:

5 Ion Stopping5.1 IntroductionWhen

- Page 61 and 62:

5.3 Nuclear Stopping 51MeV mg −1

- Page 63 and 64:

5.3 Nuclear Stopping 531−m1−2mC

- Page 65 and 66:

5.4 ZBL Nuclear Stopping Cross-Sect

- Page 67 and 68:

5.5 Electronic Stopping 575.5.1 Hig

- Page 69 and 70:

5.5 Electronic Stopping 59Table 5.1

- Page 71:

Problems 61Problems5.1 Calculate th

- Page 74 and 75:

64 6 Ion Range and Range Distributi

- Page 76 and 77:

66 6 Ion Range and Range Distributi

- Page 78 and 79:

68 6 Ion Range and Range Distributi

- Page 80 and 81:

70 6 Ion Range and Range Distributi

- Page 82 and 83:

72 6 Ion Range and Range Distributi

- Page 84 and 85:

74 6 Ion Range and Range Distributi

- Page 86 and 87:

76 6 Ion Range and Range Distributi

- Page 88 and 89:

78 7 Displacements and Radiation Da

- Page 90 and 91:

80 7 Displacements and Radiation Da

- Page 92 and 93:

82 7 Displacements and Radiation Da

- Page 94 and 95:

84 7 Displacements and Radiation Da

- Page 96 and 97:

86 7 Displacements and Radiation Da

- Page 98 and 99:

88 7 Displacements and Radiation Da

- Page 100 and 101:

90 7 Displacements and Radiation Da

- Page 102 and 103:

92 7 Displacements and Radiation Da

- Page 104 and 105:

94 8 Channeling1.00.8Non-aligned Im

- Page 106 and 107:

96 8 ChannelingMeV ION BEAMSUBSTITU

- Page 108 and 109:

98 8 ChannelingThe channeling effec

- Page 110 and 111:

100 8 Channeling4.0Silicon2.0P (mic

- Page 112 and 113:

102 8 ChannelingdσσD( ψc) = ∫

- Page 114 and 115:

104 8 ChannelingDechanneled fractio

- Page 116 and 117:

106 8 ChannelingProblems8.1 Calcula

- Page 118 and 119:

108 9 Doping, Diffusion and Defects

- Page 120 and 121:

110 9 Doping, Diffusion and Defects

- Page 122 and 123:

112 9 Doping, Diffusion and Defects

- Page 124 and 125:

114 9 Doping, Diffusion and Defects

- Page 126 and 127:

116 9 Doping, Diffusion and Defects

- Page 128 and 129:

118 9 Doping, Diffusion and Defects

- Page 130 and 131:

120 9 Doping, Diffusion and Defects

- Page 132 and 133:

122 9 Doping, Diffusion and Defects

- Page 134 and 135:

124 9 Doping, Diffusion and Defects

- Page 136 and 137:

126 9 Doping, Diffusion and Defects

- Page 138 and 139:

128 10 Crystallization and Regrowth

- Page 140 and 141:

130 10 Crystallization and Regrowth

- Page 142 and 143:

132 10 Crystallization and Regrowth

- Page 144 and 145:

134 10 Crystallization and Regrowth

- Page 146 and 147:

136 10 Crystallization and Regrowth

- Page 148 and 149:

138 10 Crystallization and Regrowth

- Page 150 and 151:

140 10 Crystallization and Regrowth

- Page 152 and 153:

142 10 Crystallization and Regrowth

- Page 154 and 155:

144 11 Si Slicing and Layer Transfe

- Page 156 and 157:

146 11 Si Slicing and Layer Transfe

- Page 158 and 159: 148 11 Si Slicing and Layer Transfe

- Page 160 and 161: 150 11 Si Slicing and Layer Transfe

- Page 162 and 163: 152 11 Si Slicing and Layer Transfe

- Page 164 and 165: 154 11 Si Slicing and Layer Transfe

- Page 166 and 167: 156 11 Si Slicing and Layer Transfe

- Page 168 and 169: 158 11 Si Slicing and Layer Transfe

- Page 170 and 171: 160 12 Surface Erosion During Impla

- Page 172 and 173: 162 12 Surface Erosion During Impla

- Page 174 and 175: 164 12 Surface Erosion During Impla

- Page 176 and 177: 166 12 Surface Erosion During Impla

- Page 178 and 179: 168 12 Surface Erosion During Impla

- Page 180 and 181: 170 12 Surface Erosion During Impla

- Page 182 and 183: 172 12 Surface Erosion During Impla

- Page 184 and 185: 174 12 Surface Erosion During Impla

- Page 186 and 187: 176 12 Surface Erosion During Impla

- Page 188 and 189: 178 12 Surface Erosion During Impla

- Page 190 and 191: 180 13 Ion-Induced Atomic Intermixi

- Page 192 and 193: 182 13 Ion-Induced Atomic Intermixi

- Page 194 and 195: 184 13 Ion-Induced Atomic Intermixi

- Page 196 and 197: 186 13 Ion-Induced Atomic Intermixi

- Page 198 and 199: 188 13 Ion-Induced Atomic Intermixi

- Page 200 and 201: 190 13 Ion-Induced Atomic Intermixi

- Page 202 and 203: 192 13 Ion-Induced Atomic Intermixi

- Page 204 and 205: 194 14 Application of Ion Implantat

- Page 206 and 207: 196 14 Application of Ion Implantat

- Page 210 and 211: 200 14 Application of Ion Implantat

- Page 212 and 213: 202 14 Application of Ion Implantat

- Page 214 and 215: 204 14 Application of Ion Implantat

- Page 216 and 217: 206 14 Application of Ion Implantat

- Page 218 and 219: 208 14 Application of Ion Implantat

- Page 220 and 221: 210 14 Application of Ion Implantat

- Page 223 and 224: 15 Ion Implantation in CMOS Technol

- Page 225 and 226: 15.2 Implanters Used in CMOS Proces

- Page 227 and 228: 15.2 Implanters Used in CMOS Proces

- Page 229 and 230: 15.2 Implanters Used in CMOS Proces

- Page 231 and 232: 15.2 Implanters Used in CMOS Proces

- Page 233 and 234: 15.3 Low Energy Productivity: Beam

- Page 235 and 236: 15.3 Low Energy Productivity: Beam

- Page 237 and 238: 15.4 Low Energy Productivity: Beam

- Page 239 and 240: 15.4 Low Energy Productivity: Beam

- Page 241 and 242: 15.4 Low Energy Productivity: Beam

- Page 243 and 244: 15.5 Angle Control 233Fig. 15.13. O

- Page 245 and 246: 15.5 Angle Control 235Fig. 15.15. I

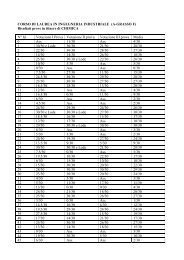

- Page 247 and 248: References 237No. of implants504540

- Page 249 and 250: Appendix ATable of the Elementselem

- Page 251 and 252: Appendix A 241elementatomicnumber(Z

- Page 253 and 254: Appendix A 243element atomicnumber(

- Page 255 and 256: Appendix A 245element atomicnumber(

- Page 257 and 258: Appendix A 247element atomicnumber(

- Page 259 and 260:

Appendix A 249element atomicnumber(

- Page 261 and 262:

Appendix A 251element atomicnumber(

- Page 263 and 264:

Appendix A 253element atomicnumber(

- Page 265 and 266:

Appendix BPhysical constants, conve

- Page 267 and 268:

IndexAlpha particle 8amorphization

- Page 269 and 270:

Index 259differential cross-section

- Page 271 and 272:

Index 261layer transfer 143Lennard-

- Page 273:

Index 263thermodynamiceffect ion be