PCT/2002/18 - World Intellectual Property Organization

PCT/2002/18 - World Intellectual Property Organization

PCT/2002/18 - World Intellectual Property Organization

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

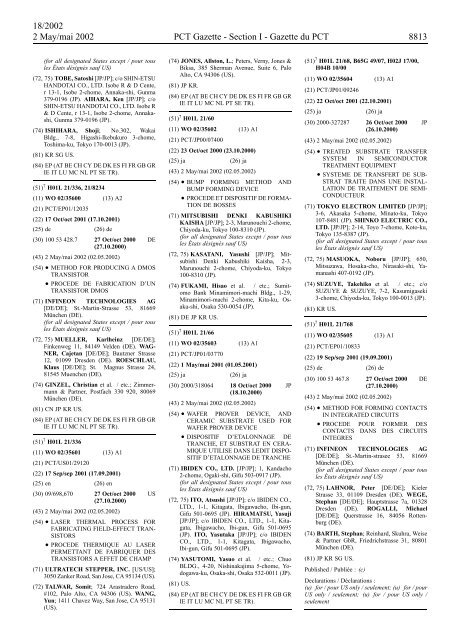

<strong>18</strong>/<strong>2002</strong><br />

2 May/mai <strong>2002</strong> <strong>PCT</strong> Gazette - Section I - Gazette du <strong>PCT</strong> 8813<br />

(for all designated States except / pour tous<br />

les États désignés sauf US)<br />

(72, 75) TOBE, Satoshi [JP/JP]; c/o SHIN-ETSU<br />

HANDOTAI CO., LTD. Isobe R & D Cente,<br />

r 13-1, Isobe 2-chome, Annaka-shi, Gunma<br />

379-0196 (JP). AIHARA, Ken [JP/JP]; c/o<br />

SHIN-ETSU HANDOTAI CO., LTD. Isobe R<br />

& D Cente, r 13-1, Isobe 2-chome, Annakashi,<br />

Gunma 379-0196 (JP).<br />

(74) ISHIHARA, Shoji; No.302, Wakai<br />

Bldg., 7-8, Higashi-Ikebukuro 3-chome,<br />

Toshima-ku, Tokyo 170-0013 (JP).<br />

(81) KR SG US.<br />

(84) EP (AT BE CH CY DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE TR).<br />

(51) 7 H01L 21/336, 21/8234<br />

(11) WO 02/35600<br />

(21) <strong>PCT</strong>/EP01/12035<br />

(13) A2<br />

(22) 17 Oct/oct 2001 (17.10.2001)<br />

(25) de (26) de<br />

(30) 100 53 428.7 27 Oct/oct 2000<br />

(27.10.2000)<br />

DE<br />

(43) 2 May/mai <strong>2002</strong> (02.05.<strong>2002</strong>)<br />

(54) METHOD FOR PRODUCING A DMOS<br />

TRANSISTOR<br />

PROCEDE DE FABRICATION D’UN<br />

TRANSISTOR DMOS<br />

(71) INFINEON TECHNOLOGIES AG<br />

[DE/DE]; St.-Martin-Strasse 53, 81669<br />

München (DE).<br />

(for all designated States except / pour tous<br />

les États désignés sauf US)<br />

(72, 75) MUELLER, Karlheinz [DE/DE];<br />

Finkenweg 11, 84149 Velden (DE). WAG-<br />

NER, Cajetan [DE/DE]; Bautzner Strasse<br />

12, 01099 Dresden (DE). ROESCHLAU,<br />

Klaus [DE/DE]; St.<br />

81545 Muenchen (DE).<br />

Magnus Strasse 24,<br />

(74) GINZEL, Christian et al. / etc.; Zimmermann<br />

& Partner, Postfach 330 920, 80069<br />

München (DE).<br />

(81) CN JP KR US.<br />

(84) EP (AT BE CH CY DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE TR).<br />

(51) 7 H01L 21/336<br />

(11) WO 02/35601 (13) A1<br />

(21) <strong>PCT</strong>/US01/29120<br />

(22) 17 Sep/sep 2001 (17.09.2001)<br />

(25) en (26) en<br />

(30) 09/698,670 27 Oct/oct 2000 US<br />

(27.10.2000)<br />

(43) 2 May/mai <strong>2002</strong> (02.05.<strong>2002</strong>)<br />

(54) LASER THERMAL PROCESS FOR<br />

FABRICATING FIELD-EFFECT TRAN-<br />

SISTORS<br />

PROCEDE THERMIQUE AU LASER<br />

PERMETTANT DE FABRIQUER DES<br />

TRANSISTORS A EFFET DE CHAMP<br />

(71) ULTRATECH STEPPER, INC. [US/US];<br />

3050 Zanker Road, San Jose, CA 95134 (US).<br />

(72) TALWAR, Somit; 724 Arastradero Road,<br />

#102, Palo Alto, CA 94306 (US). WANG,<br />

Yun; 1411 Chavez Way, San Jose, CA 95131<br />

(US).<br />

(74) JONES, Allston, L.; Peters, Verny, Jones &<br />

Biksa, 385 Sherman Avenue, Suite 6, Palo<br />

Alto, CA 94306 (US).<br />

(81) JP KR.<br />

(84) EP (AT BE CH CY DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE TR).<br />

(51) 7 H01L 21/60<br />

(11) WO 02/35602 (13) A1<br />

(21) <strong>PCT</strong>/JP00/07400<br />

(22) 23 Oct/oct 2000 (23.10.2000)<br />

(25) ja (26) ja<br />

(43) 2 May/mai <strong>2002</strong> (02.05.<strong>2002</strong>)<br />

(54) BUMP FORMING METHOD AND<br />

BUMP FORMING DEVICE<br />

PROCEDE ET DISPOSITIF DE FORMA-<br />

TION DE BOSSES<br />

(71) MITSUBISHI DENKI KABUSHIKI<br />

KAISHA [JP/JP]; 2-3, Marunouchi 2-chome,<br />

Chiyoda-ku, Tokyo 100-8310 (JP).<br />

(for all designated States except / pour tous<br />

les États désignés sauf US)<br />

(72, 75) KASATANI, Yasushi [JP/JP]; Mitsubishi<br />

Denki Kabushiki Kaisha, 2-3,<br />

Marunouchi 2-chome, Chiyoda-ku, Tokyo<br />

100-8310 (JP).<br />

(74) FUKAMI, Hisao et al. / etc.; Sumitomo<br />

Bank Minamimori-machi Bldg., 1-29,<br />

Minamimori-machi 2-chome, Kita-ku, Osaka-shi,<br />

Osaka 530-0054 (JP).<br />

(81) DE JP KR US.<br />

(51) 7 H01L 21/66<br />

(11) WO 02/35603 (13) A1<br />

(21) <strong>PCT</strong>/JP01/03770<br />

(22) 1 May/mai 2001 (01.05.2001)<br />

(25) ja (26) ja<br />

(30) 2000/3<strong>18</strong>064 <strong>18</strong> Oct/oct 2000 JP<br />

(<strong>18</strong>.10.2000)<br />

(43) 2 May/mai <strong>2002</strong> (02.05.<strong>2002</strong>)<br />

(54) WAFER PROVER DEVICE, AND<br />

CERAMIC SUBSTRATE USED FOR<br />

WAFER PROVER DEVICE<br />

DISPOSITIF D’ETALONNAGE DE<br />

TRANCHE, ET SUBSTRAT EN CERA-<br />

MIQUE UTILISE DANS LEDIT DISPO-<br />

SITIF D’ETALONNAGE DE TRANCHE<br />

(71) IBIDEN CO., LTD. [JP/JP]; 1, Kandacho<br />

2-chome, Ogaki-shi, Gifu 503-0917 (JP).<br />

(for all designated States except / pour tous<br />

les États désignés sauf US)<br />

(72, 75) ITO, Atsushi [JP/JP]; c/o IBIDEN CO.,<br />

LTD., 1-1, Kitagata, Ibigawacho, Ibi-gun,<br />

Gifu 501-0695 (JP). HIRAMATSU, Yasuji<br />

[JP/JP]; c/o IBIDEN CO., LTD., 1-1, Kitagata,<br />

Ibigawacho, Ibi-gun, Gifu 501-0695<br />

(JP). ITO, Yasutaka [JP/JP]; c/o IBIDEN<br />

CO., LTD., 1-1, Kitagata, Ibigawacho,<br />

Ibi-gun, Gifu 501-0695 (JP).<br />

(74) YASUTOMI, Yasuo et al. / etc.; Chuo<br />

BLDG., 4-20, Nishinakajima 5-chome, Yodogawa-ku,<br />

Osaka-shi, Osaka 532-0011 (JP).<br />

(81) US.<br />

(84) EP (AT BE CH CY DE DK ES FI FR GB GR<br />

IE IT LU MC NL PT SE TR).<br />

(51) 7 H01L 21/68, B65G 49/07, H02J 17/00,<br />

H04B 10/00<br />

(11) WO 02/35604 (13) A1<br />

(21) <strong>PCT</strong>/JP01/09246<br />

(22) 22 Oct/oct 2001 (22.10.2001)<br />

(25) ja (26) ja<br />

(30) 2000-327287 26 Oct/oct 2000 JP<br />

(26.10.2000)<br />

(43) 2 May/mai <strong>2002</strong> (02.05.<strong>2002</strong>)<br />

(54) TREATED SUBSTRATE TRANSFER<br />

SYSTEM IN SEMICONDUCTOR<br />

TREATMENT EQUIPMENT<br />

SYSTEME DE TRANSFERT DE SUB-<br />

STRAT TRAITE DANS UNE INSTAL-<br />

LATION DE TRAITEMENT DE SEMI-<br />

CONDUCTEUR<br />

(71) TOKYO ELECTRON LIMITED [JP/JP];<br />

3-6, Akasaka 5-chome, Minato-ku, Tokyo<br />

107-8481 (JP). SHINKO ELECTRIC CO.,<br />

LTD. [JP/JP]; 2-14, Toyo 7-chome, Koto-ku,<br />

Tokyo 135-8387 (JP).<br />

(for all designated States except / pour tous<br />

les États désignés sauf US)<br />

(72, 75) MASUOKA, Noboru [JP/JP]; 650,<br />

Mitsuzawa, Hosaka-cho, Nirasaki-shi, Yamanashi<br />

407-0192 (JP).<br />

(74) SUZUYE, Takehiko et al. / etc.; c/o<br />

SUZUYE & SUZUYE, 7-2, Kasumigaseki<br />

3-chome, Chiyoda-ku, Tokyo 100-0013 (JP).<br />

(81) KR US.<br />

(51) 7 H01L 21/768<br />

(11) WO 02/35605<br />

(21) <strong>PCT</strong>/EP01/10833<br />

(13) A1<br />

(22) 19 Sep/sep 2001 (19.09.2001)<br />

(25) de (26) de<br />

(30) 100 53 467.8 27 Oct/oct 2000<br />

(27.10.2000)<br />

DE<br />

(43) 2 May/mai <strong>2002</strong> (02.05.<strong>2002</strong>)<br />

(54) METHOD FOR FORMING CONTACTS<br />

IN INTEGRATED CIRCUITS<br />

PROCEDE POUR FORMER DES<br />

CONTACTS<br />

INTEGRES<br />

DANS DES CIRCUITS<br />

(71) INFINEON TECHNOLOGIES AG<br />

[DE/DE]; St.-Martin-strasee 53, 81669<br />

München (DE).<br />

(for all designated States except / pour tous<br />

les États désignés sauf US)<br />

(72, 75) LAHNOR, Peter [DE/DE]; Kieler<br />

Strasse 33, 01109 Dresden (DE). WEGE,<br />

Stephan [DE/DE]; Hauptstrasse 7a, 01328<br />

Dresden (DE). ROGALLI, Michael<br />

[DE/DE]; Querstrasse 16,<br />

burg (DE).<br />

84056 Rotten-<br />

(74) BARTH, Stephan; Reinhard, Skuhra, Weise<br />

& Partner GbR, Friedrichstrasse 31, 80801<br />

München (DE).<br />

(81) JP KR SG US.<br />

Published / Publiée :(c)<br />

Declarations / Déclarations :<br />

(u) for / pour US only / seulement; (u) for / pour<br />

US only / seulement; (u) for / pour US only /<br />

seulement