Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

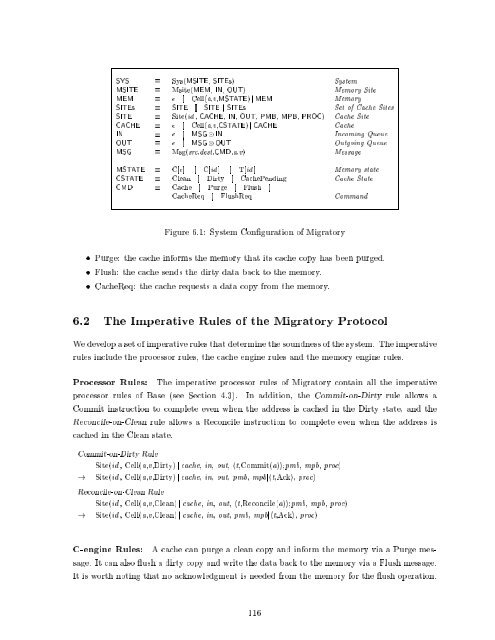

SYS Sys(MSITE, SITEs) System<br />

MSITE Msite(MEM, IN, OUT) Memory Site<br />

MEM [] Cell(a,v,MSTATE) j MEM Memory<br />

SITEs SITE [] SITE j SITEs Set <strong>of</strong> <strong>Cache</strong> Sites<br />

SITE Site(id , CACHE, IN, OUT, PMB, MPB, PROC) <strong>Cache</strong> Site<br />

CACHE [] Cell(a,v,CSTATE) j CACHE <strong>Cache</strong><br />

IN [] MSG IN Incoming Queue<br />

OUT [] MSG OUT Outgoing Queue<br />

MSG Msg(src,dest,CMD,a,v) Message<br />

MSTATE C[ ] [] C[id ] [] T[id ] Memory state<br />

CSTATE Clean [] Dirty [] <strong>Cache</strong>Pending <strong>Cache</strong> State<br />

CMD <strong>Cache</strong> [] Purge [] Flush []<br />

<strong>Cache</strong>Req [] FlushReq Comm<strong>and</strong><br />

Figure 6.1: System Con guration <strong>of</strong> Migratory<br />

Purge: the cache informs the memory that its cache copy has been purged.<br />

Flush: the cache sends the dirty databack to the memory.<br />

<strong>Cache</strong>Req: the cache requests a data copy from the memory.<br />

6.2 The Imperative Rules <strong>of</strong> the Migratory Protocol<br />

We develop a set <strong>of</strong> imperative rules that determine the soundness <strong>of</strong> the system. The imperative<br />

rules include the processor rules, the cache engine rules <strong>and</strong> the memory engine rules.<br />

Processor Rules: The imperative processor rules <strong>of</strong> Migratory contain all the imperative<br />

processor rules <strong>of</strong> Base (see Section 4.3). In addition, the Commit-on-Dirty rule allows a<br />

Commit instruction to complete even when the address is cached in the Dirty state, <strong>and</strong> the<br />

Reconcile-on-Clean rule allows a Reconcile instruction to complete even when the address is<br />

cached in the Clean state.<br />

Commit-on-Dirty Rule<br />

Site(id , Cell(a,v,Dirty) j cache, in, out, ht,Commit(a)ipmb, mpb, proc)<br />

! Site(id , Cell(a,v,Dirty) j cache, in, out, pmb, mpbjht,Acki, proc)<br />

Reconcile-on-Clean Rule<br />

Site(id , Cell(a,v,Clean) j cache, in, out, ht,Reconcile(a)ipmb, mpb, proc)<br />

! Site(id , Cell(a,v,Clean) j cache, in, out, pmb, mpbjht,Acki, proc)<br />

C-engine Rules: Acache can purge a clean copy <strong>and</strong> inform the memory via a Purge mes-<br />

sage. It can also ush a dirty copy <strong>and</strong> write the data back to the memory via a Flush message.<br />

It is worth noting that no acknowledgment is needed from the memory for the ush operation.<br />

116