Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

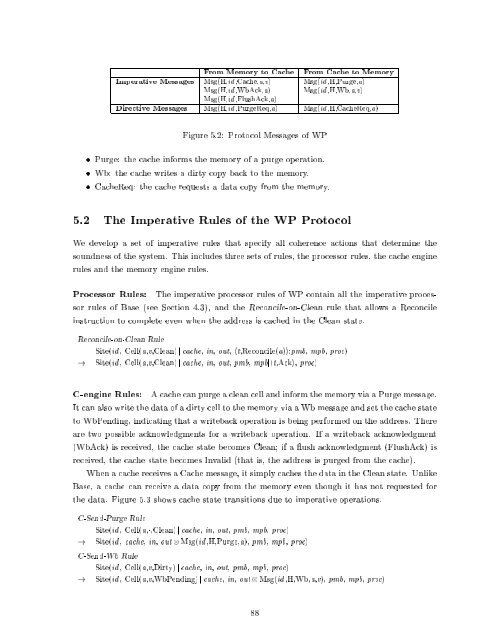

From Memory to <strong>Cache</strong> From <strong>Cache</strong> to Memory<br />

Imperative Messages Msg(H,id ,<strong>Cache</strong>,a,v) Msg(id ,H,Purge,a)<br />

Msg(H,id ,WbAck,a) Msg(id ,H,Wb,a,v)<br />

Msg(H,id ,FlushAck,a)<br />

Directive Messages Msg(H,id ,PurgeReq,a) Msg(id ,H,<strong>Cache</strong>Req,a)<br />

Figure 5.2: Protocol Messages <strong>of</strong> WP<br />

Purge: the cache informs the memory <strong>of</strong> a purge operation.<br />

Wb: the cache writes a dirty copy back tothememory.<br />

<strong>Cache</strong>Req: the cache requests a data copy from the memory.<br />

5.2 The Imperative Rules <strong>of</strong> the WP Protocol<br />

We develop a set <strong>of</strong> imperative rules that specify all coherence actions that determine the<br />

soundness <strong>of</strong> the system. This includes three sets <strong>of</strong> rules, the processor rules, the cache engine<br />

rules <strong>and</strong> the memory engine rules.<br />

Processor Rules: The imperative processor rules <strong>of</strong> WP contain all the imperative proces-<br />

sor rules <strong>of</strong> Base (see Section 4.3), <strong>and</strong> the Reconcile-on-Clean rule that allows a Reconcile<br />

instruction to complete even when the address is cached in the Clean state.<br />

Reconcile-on-Clean Rule<br />

Site(id , Cell(a,v,Clean) j cache, in, out, ht,Reconcile(a)ipmb, mpb, proc)<br />

! Site(id , Cell(a,v,Clean) j cache, in, out, pmb, mpbjht,Acki, proc)<br />

C-engine Rules: Acache can purge a clean cell <strong>and</strong> inform the memory via a Purge message.<br />

It can also write the data <strong>of</strong> a dirty cell to the memory via a Wb message <strong>and</strong> set the cache state<br />

to WbPending, indicating that a writeback operation is being performed on the address. There<br />

are two possible acknowledgments for a writeback operation. If a writeback acknowledgment<br />

(WbAck) is received, the cache state becomes Clean if a ush acknowledgment (FlushAck) is<br />

received, the cache state becomes Invalid (that is, the address is purged from the cache).<br />

When a cache receives a <strong>Cache</strong> message, it simply caches the data in the Clean state. Unlike<br />

Base, a cache can receive a data copy from the memory even though it has not requested for<br />

the data. Figure 5.3 shows cache state transitions due to imperative operations.<br />

C-Send-Purge Rule<br />

Site(id , Cell(a,-,Clean) j cache, in, out, pmb, mpb, proc)<br />

! Site(id , cache, in, out Msg(id ,H,Purge,a), pmb, mpb, proc)<br />

C-Send-Wb Rule<br />

Site(id , Cell(a,v,Dirty) j cache, in, out, pmb, mpb, proc)<br />

! Site(id , Cell(a,v,WbPending) j cache, in, out Msg(id ,H,Wb,a,v), pmb, mpb, proc)<br />

88