Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Design and Verification of Adaptive Cache Coherence Protocols ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

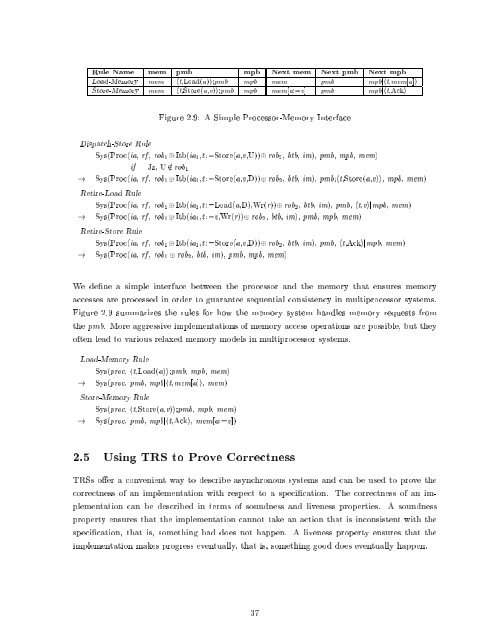

Rule Name mem pmb mpb Next mem Next pmb Next mpb<br />

Load-Memory mem ht,Load(a)ipmb mpb mem pmb mpbjht,mem[a]i<br />

Store-Memory mem ht,Store(a,v)ipmb mpb mem[a:=v] pmb mpbjht,Acki<br />

Figure 2.9: A Simple Processor-Memory Interface<br />

Dispatch-Store Rule<br />

Sys(Proc(ia, rf , rob1 Itb(ia1,t :=Store(a,v,U)) rob2, btb, im), pmb, mpb, mem)<br />

if Jz, U =2 rob1<br />

! Sys(Proc(ia, rf , rob1 Itb(ia1,t :=Store(a,v,D)) rob2, btb, im), pmbht,Store(a,v)i, mpb, mem)<br />

Retire-Load Rule<br />

Sys(Proc(ia, rf , rob1 Itb(ia1,t :=Load(a,D),Wr(r)) rob2, btb, im), pmb, ht,vijmpb, mem)<br />

! Sys(Proc(ia, rf , rob1 Itb(ia1,t :=v,Wr(r)) rob2, btb, im), pmb, mpb, mem)<br />

Retire-Store Rule<br />

Sys(Proc(ia, rf , rob1 Itb(ia1,t :=Store(a,v,D)) rob2, btb, im), pmb, ht,Ackijmpb, mem)<br />

! Sys(Proc(ia, rf , rob1 rob2, btb, im), pmb, mpb, mem)<br />

We de ne a simple interface between the processor <strong>and</strong> the memory that ensures memory<br />

accesses are processed in order to guarantee sequential consistency in multiprocessor systems.<br />

Figure 2.9 summarizes the rules for how the memory system h<strong>and</strong>les memory requests from<br />

the pmb. More aggressive implementations <strong>of</strong> memory access operations are possible, but they<br />

<strong>of</strong>ten lead to various relaxed memory models in multiprocessor systems.<br />

Load-Memory Rule<br />

Sys(proc, ht,Load(a)ipmb, mpb, mem)<br />

! Sys(proc, pmb, mpbjht,mem[a]i, mem)<br />

Store-Memory Rule<br />

Sys(proc, ht,Store(a,v)ipmb, mpb, mem)<br />

! Sys(proc, pmb, mpbjht,Acki, mem[a:=v])<br />

2.5 Using TRS to Prove Correctness<br />

TRSs o er a convenient way to describe asynchronous systems <strong>and</strong> can be used to prove the<br />

correctness <strong>of</strong> an implementation with respect to a speci cation. The correctness <strong>of</strong> an im-<br />

plementation can be described in terms <strong>of</strong> soundness <strong>and</strong> liveness properties. A soundness<br />

property ensures that the implementation cannot take an action that is inconsistent with the<br />

speci cation, that is, something bad does not happen. A liveness property ensures that the<br />

implementation makes progress eventually, that is, something good does eventually happen.<br />

37